# QT3310 3U VPX 导冷 / 风冷 SATA 存储控制板

## 产品手册

Ver. 2016. 5.18

#### 概述

QT3310 风冷 / 导冷高速大容量存储板卡是一种海量数据 实时记录与存储装置,可以为产品的多种数据提供记录、存储、 下载,读写访问等功能。

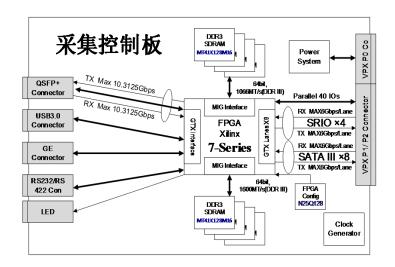

基于 Xilinx 7-Series FPGA 平台的 3U VPX 高速数据存储控制板,可以提供风冷和导冷两种物理结构形式,搭配一张或者两张存储子板(SATA SSD 板),可以实现各种类型(如4路自定义最高 10Gbps 光口,4~8路最高 6.5Gbps 背板 Rokect IO 的 Serdes 数据,可配置成一组或者两组 SRIO x4)的数据输入的即时存储。每张存储子板支持最大 16T 存储容量,一个数据存储控制板搭配两张存储子板,最高可以实现持续 3.8GB/s,最低不低于 3.2GB/s 的存储性能,以及最大 32T的存储容量。搭配单张存储子板,可以实现持续 1.9GB/s,最低不低于 1.6GB/s 的存储性能,以及最大 16T 的存储容量。

#### 模块框图

#### 规格:

- ▶ 用户可编程的 Xilinx® Kintex® 7 325T/410T FPGA;

- ➤ 双通道 2GB/256Meg x 16 DDR3 内存;

- ▶ 1路 40Gbps 的 QSFP+ Cage, 支持光纤转换成 标准的 4路 10Gbps 的 SFP+;

- ▶ VPX 3U 导冷结构设计,符合 VITA48 REDI标准, 完全兼容风冷结构,直接更换结构件即可;

- 支持 GE、RS232、RS422、GPIO等接口控制, 以及 GE 接口导出,存储子卡可选快导版本,单张 存储子卡导出速度可达 2GB/s,系统搭配两张存储 子板导出速度可达 4GB/s,可选支持 USB3.0 导出, GE 接口还可以支持数据快视和数据输入功能;

- ▶ 提供20路LVDS信号,可配置为40路LVTTL25/LVCMOS25/LVTTL33/LVCMOS33单端信号:

- 符合 Open VPX 标准, MOD3-PAY-2F1F2U-16.2.1-n;

- ▶ 提供 Windows® 操作系统平台驱动:

- ▶ 坚固型结构设计和高等级全加固型的连接器选型;

- ➤ 支持外置按钮输入、GPIO,记录仪可脱离上位机 单独使用:

- 可以多台采集控制板集群组网使用,使用同一个上位机软件来集群管理,成倍的增加存储容量和性能;

- 异常掉电数据恢复功能。设备能确保当前正在记录的文件数据不丢失,并在下次模块开电后,自动或者手动恢复文件。

#### 应用:

- > 实时信号存储分析

- ▶ 工业相机,无人机吊舱等图像数据采集存储

- ▶ 雷达接收器数据存储备份

- 激光雷达等

#### 支持:

▶ 支持 Windows7 和 XP 驱动和软件示例代码;

#### **FPGA**

- 3U-VPX-KC 配 置 Xilinx Kintex 7 325T/410T 系 列 FPGA, 只有少量的逻辑用作与外围 DDR3 存储器通信, 剩 余大量的逻辑资源供用户二次开发使用。

- Xilinx Kintex 7 325T 包含 326080 个 Logic Cells, 840

- 个 DSP Slices, 445 个 Block RAM(32Kb)。 Xilinx Kintex 7 410T 包 含 406720 个 Logic Cells, 1540 个 DSP Slices, 795 个 Block RAM(32Kb)

#### DDR3 存储器

3U-VPX-KC 存储器选用8片MT41J256M16HA-093, 256Meg x 16 DDR3 SDRAM, 最大数据率 1600Mbps。

#### FLASH 存储器

选用外挂 FLASH 的形式, QSPI (x4) 配置模式, 128MB 容量 的 NOR FLASH。

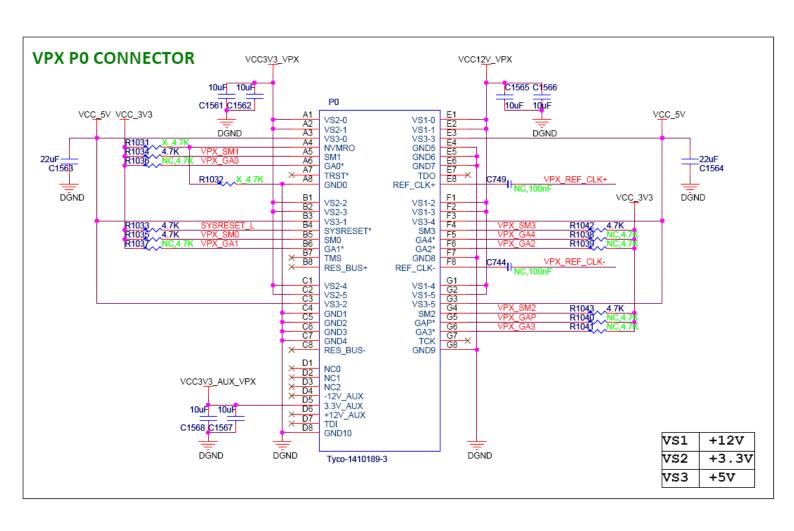

#### 存储控制模块的 VPX 接口定义

#### VPX P0

#### 物理条件定义表

|      | ~                |                  |  |  |

|------|------------------|------------------|--|--|

| 环境   | A 级              | B 级              |  |  |

| 操作温度 | 0° ~70°          | -40° ~85°        |  |  |

| 存储温度 | -50°C ~1125°C    | -50°C ~1125°C    |  |  |

| 湿度操作 | 0~100% 不冷凝       | 0~100% 不冷凝       |  |  |

| 存储湿度 | 0~100%           | 0~100%           |  |  |

| 振动随机 | 0.1g2/Hz 10-3kHz | 0.1g2/Hz 10-3kHz |  |  |

| 抗冲击性 | 最大 30g           | 最大 30g           |  |  |

| 图层   | 没有               | 保型               |  |  |

## VPX P1

| Plug_In P. C | D D        | Row E      |            | n n        | D 0        | Row B      |            | ъ          |            |

|--------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Module P1    | Row G      | Row F      | EVEN       | ODD        | Row D      | Row C      | EVEN       | ODD        | Row A      |

| Bplane J1    | Row i      | Row h      | Row g      | Row f      | Row e      | Row d      | Row c      | Row b      | Row a      |

| 1            | RSV        | GND        | GND_J1     | DP01_TD0_N | DP01_TD0_P | GND        | GND_J1     | DP01_RD0_N | DP01_RD0_P |

| 2            | GND        | DP01_TD1_N | DP01_TD1_P | GND_J1     | GND        | DP01_RD1_N | DP01_RD1_P | GND_J1     | GND        |

| 3            | P1_VBAT    | GND        | GND_J1     | DP01_TD2_N | DP01_TD2_P | GND        | GND_J1     | DP01_RD2_N | DP01_RD2_P |

| 4            | GND        | DP01_TD3_N | DP01_TD3_P | GND_J1     | GND        | DP01_RD3_N | DP01_RD3_P | GND_J1     | GND        |

| 5            | SYS_CON*   | GND        | GND_J1     | DP02_TD0_N | DP02_TD0_P | GND        | GND_J1     | DP02_RD0_N | DP02_RD0_P |

| 6            | GND        | DP02_TD0_N | DP02_TD0_P | GND_J1     | GND        | DP02_RD1_N | DP02_RD1_P | GND_J1     | GND        |

| 7            | REF_CLK_SE | GND        | GND_J1     | DP02_TD0_N | DP02_TD0_P | GND        | GND_J1     | DP02_RD2_N | DP02_RD2_P |

| 8            | GND        | DP02_TD0_N | DP02_TD0_P | GND_J1     | GND        | DP02_RD3_N | DP02_RD3_P | GND_J1     | GND        |

| 9            | SE         | GND        | GND_J1     | DP03_TD0_N | DP03_TD0_P | GND        | GND_J1     | DP03_RD0_N | DP03_RD0_P |

| 10           | GND        | DP03_TD1_N | DP03_TD1_P | GND_J1     | GND        | DP03_RD1_N | DP03_RD1_P | GND_J1     | GND        |

| 11           | SE         | GND        | GND_J1     | DP03_TD2_N | DP03_TD2_P | GND        | GND_J1     | DP03_RD2_N | DP03_RD2_P |

| 12           | GND        | DP03_TD3_N | DP03_TD3_P | GND_J1     | GND        | DP03_RD3_N | DP03_RD3_P | GND_J1     | GND        |

| 13           | SE         | GND_J1     | GND        | DP04_TD0_N | DP04_TD0_P | GND_J1     | GND        | DP04_RD0_N | DP04_RD0_P |

| 14           | GND        | DP04_TD1_N | DP04_TD1_P | GND_J1     | GND        | DP04_RD1_N | DP04_RD1_P | GND_J1     | GND        |

| 15           | SE         | GND_J1     | GND        | DP04_TD2_N | DP04_TD2_P | GND_J1     | GND        | DP04_RD2_N | DP04_RD2_P |

| 16           | GND        | DP04_TD3_N | DP04_TD3_P | GND_J1     | GND        | DP04_RD3_N | DP04_RD3_P | GND_J1     | GND        |

## 信号说明

| DP01_RDx+, DP01_RDx- | Data Plane 1 的接收信号,差分,用于与 SSD 存储模块卡通信。<br>连接到 GTX |

|----------------------|---------------------------------------------------|

| DP01_TDx+,DP01_TDx-  | Data Plane 1 的发送信号,差分,用于与 SSD 存储模块卡通信。<br>连接到 GTX |

| DP02_RDx+,DP02_RDx-  | Data Plane 2 的接收信号,差分,用于与 SSD 存储模块卡通信。<br>连接到 GTX |

| DP02_TDx+,DP02_TDx-  | Data Plane 2 的发送信号,差分,用于与 SSD 存储模块卡通信。<br>连接到 GTX |

| DP03_RDx+,DP03_RDx-  | Data Plane 2 的接收信号,差分,用于与 ADC 采集模块卡通信。<br>连接到 GTX |

| DP03_TDx+,DP03_TDx-  | Data Plane 2 的发送信号,差分,用于与 ADC 采集模块卡通信。<br>连接到 GTX |

| DP04_RDx+, DP04_RDx- | 无                                                 |

| DP04_TDx+, DP04_TDx- | 无                                                 |

## VPX P1

| Plug_In   | Plug_In P C | р р         | Row E       |            | D D        |             | Row B       |            |            |

|-----------|-------------|-------------|-------------|------------|------------|-------------|-------------|------------|------------|

| Module P1 | Row G       | Row F       | EVEN        | ODD        | Row D      | Row C       | EVEN        | ODD        | Row A      |

| Bplane J1 | Row i       | Row h       | Row g       | Row f      | Row e      | Row d       | Row c       | Row b      | Row a      |

| 1         | JTAG_TCK    | GND         | GND_J1      | P2_D1_N    | P2_D1_P    | GND         | GND_J1      | P2_D0_N    | P2_D0_P    |

| 2         | GND         | P2_D3_N     | P2_D3_P     | GND_J1     | GND        | P2_D2_N     | P2_D2_P     | GND_J1     | GND        |

| 3         | JTAG_TMS    | GND         | GND_J1      | P2_D5_N    | P2_D5_P    | GND         | GND_J1      | P2_D4_N    | P2_D4_P    |

| 4         | GND         | P2_D7_N     | P2_D7_P     | GND_J1     | GND        | P2_D6_N     | P2_D6_P     | GND_J1     | GND        |

| 5         | JTAG_TDI    | GND         | GND_J1      | P2_D9_N    | P2_D9_P    | GND         | GND_J1      | P2_D8_N    | P2_D8_P    |

| 6         | GND         | P2_D11_N    | P2_D11_P    | GND_J1     | GND        | P2_D10_N    | P2_D10_P    | GND_J1     | GND        |

| 7         | JTAG_TDO    | GND         | GND_J1      | P2_D13_N   | P2_D13_P   | GND         | GND_J1      | P2_D12_N   | P2_D12_P   |

| 8         | GND         | P2_D15_N    | P2_D15_P    | GND_J1     | GND        | P2_D14_N    | P2_D14_P    | GND_J1     | GND        |

| 9         | SE          | GND         | GND_J1      | P2_D17_N   | P2_D17_P   | GND         | GND_J1      | P2_D16_N   | P2_D16_P   |

| 10        | GND         | P2_D19_N    | P2_D19_P    | GND_J1     | GND        | P2_D18_N    | P2_D18_P    | GND_J1     | GND        |

| 11        | SE          | GND         | GND_J1      | P2_D21_N   | P2_D21_P   | GND         | GND_J1      | P2_D20_N   | P2_D20_P   |

| 12        | GND         | P2_D23_N    | P2_D23_P    | GND_J1     | GND        | P2_D22_N    | P2_D22_P    | GND_J1     | GND        |

| 13        | SE          | GND_J1      | GND         | ETH_D1_N   | ETH_D1_P   | GND_J1      | GND         | ETH_DO_N   | ETH_DO_P   |

| 14        | GND         | ETH_D3_N    | ETH_D3_P    | GND_J1     | GND        | ETH_D2_N    | ETH_D2_P    | GND_J1     | GND        |

| 15        | SE          | GND_J1      | GND         | USB_SSTX_N | USB_SSTX_P | GND_J1      | GND         | USB_SSRX_N | USB_SSRX_P |

| 16        | GND         | RS422_TXD_N | RS422_TXD_P | GND_J1     | GND        | RS422_RXD_N | RS422_RXD_P | GND_J1     | GND        |

## 信号说明

| P2_Dx_P,P2_Dx_N      | 连接到 FPGA 的 BANK 的 LVDS 信号,或者 2.5V/3.3V 单端信号 |

|----------------------|---------------------------------------------|

| JTAG_TCK, JTAG_TMS   | VPX-P2 连接器上引出的 FPGA -JTAG 调试口               |

| JTAG_TDI, JTAG_TDO   |                                             |

| ETH_Dx+, ETH_Dx-     | 千兆以太网接口信号                                   |

| ETH_LED1, ETH_LED2   | 千兆网指示灯,预留                                   |

| USB_SSTX+, USB_SSTX- | USB3.0 数据信号,发送                              |

| USB_SSRX+, USB_SSRX- | USB3.0 数据信号,接收                              |

| RS422_TX+,RS422_TX-  | RS422 接口信号,发送                               |

| RS422_RX+,RS422_RX-  | RS422 接口信号,接收                               |

#### FPGA 选项

| 风冷                | 结构导冷              |  |  |

|-------------------|-------------------|--|--|

| 3U-VPX-KC-001T    | 3U-VPX-KC-003T    |  |  |

| XC7K325T-2FFG900I | XC7K325T-2FFG900I |  |  |

| 3U-VPX-KC-002T    | 3U-VPX-KC-004T    |  |  |

| XC7K410T-2FFG900I | XC7K410T-2FFG900I |  |  |

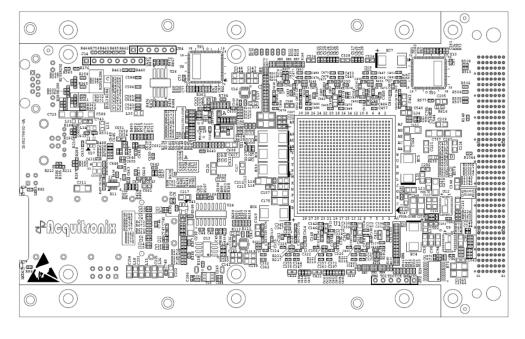

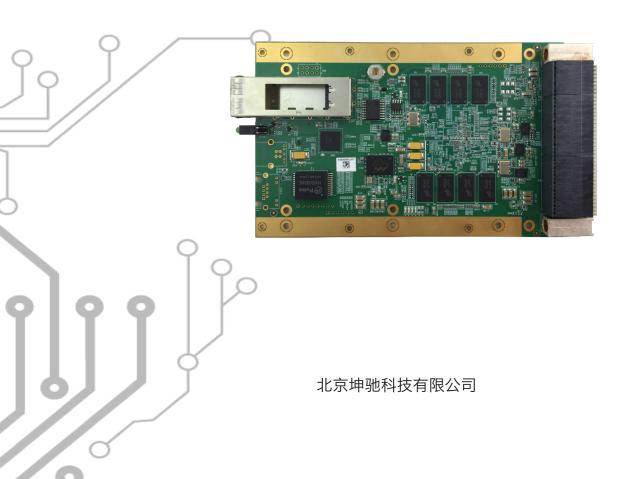

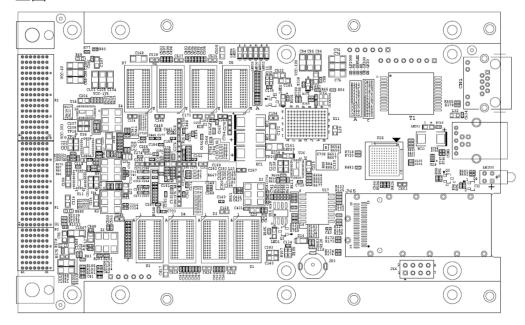

#### 板卡布局图

#### 正面

#### 背面