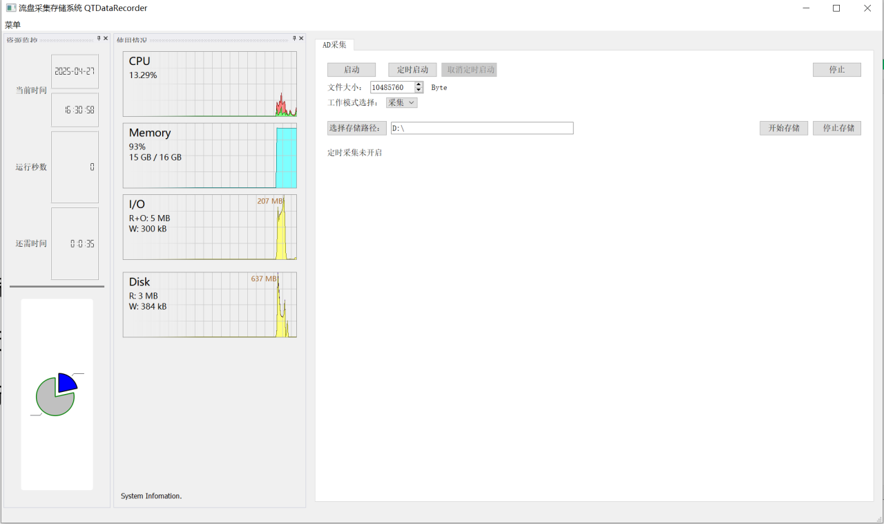

2GSPS高速采集以及毛刺檢測(cè)系統(tǒng)

采集系統(tǒng)規(guī)格:

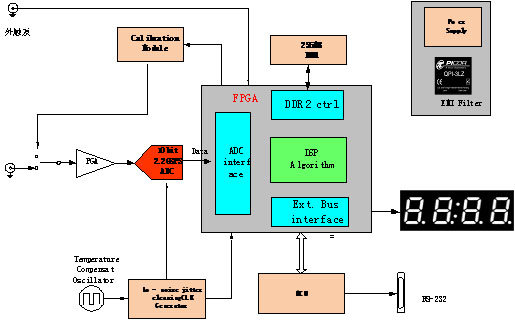

系統(tǒng)采用基于FPGA的采集加數(shù)據(jù)分析系統(tǒng),包括如下幾個(gè)部分:

1.10bit2.2GSPSADC,單通道。采樣率可以通過(guò)軟件設(shè)置。

2.低噪聲模擬前端,支持+/-5V~+/-200mV信號(hào)輸入,50Ω阻抗BNC接口。

3.板載256MBDDR2內(nèi)存。

4.優(yōu)化的USB2.0傳輸接口,支持33MB/s的連續(xù)傳輸速率。

5.支持外部觸發(fā)輸入。

6.16個(gè)可編程GPIO,可用于系統(tǒng)控制。

7.高穩(wěn)定度,超低低抖動(dòng)時(shí)鐘發(fā)生器。

8.低噪聲電源設(shè)計(jì)。

9.板載高精度自適應(yīng)校準(zhǔn)電路及算法。

10.LED顯示,指示毛刺數(shù)量和狀態(tài)。

11.毛刺電平輸出,兼容TTL電平。

12.FPGA實(shí)現(xiàn)實(shí)時(shí)毛刺檢測(cè)算法功能。

13.采集數(shù)據(jù)時(shí)間戳功能。

14.用戶可通過(guò)小鍵盤(pán)或串口進(jìn)行參數(shù)配置和模式選擇。

15.寬溫設(shè)計(jì)-20℃~+90℃

16.供電需求,單電源12DC輸入,1A電流。

17.外形尺寸:180mmX90mm

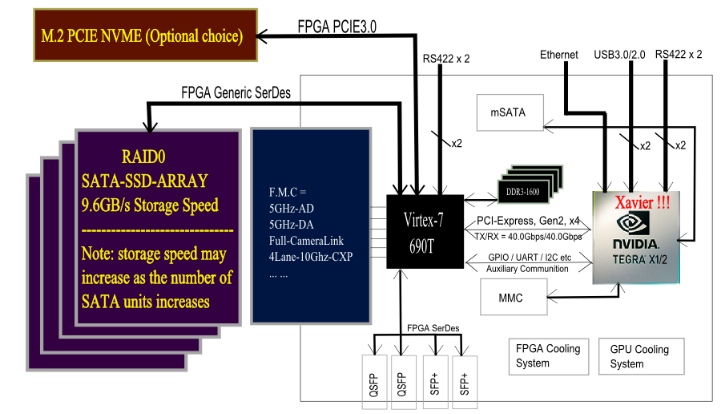

系統(tǒng)整體框圖如下:

方案描述:

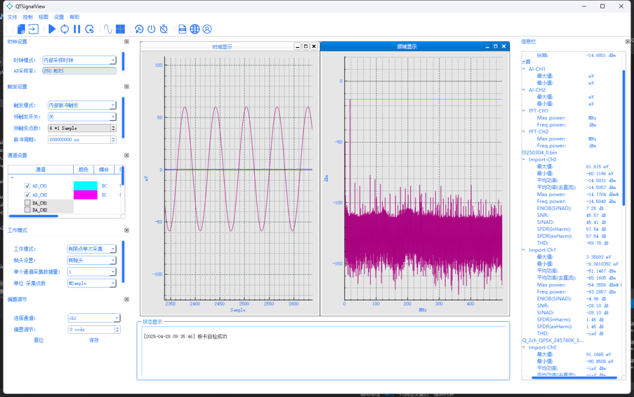

該采集系統(tǒng)主要用于長(zhǎng)時(shí)間采集1通道脈沖信號(hào):

1.采集脈沖信號(hào),實(shí)時(shí)檢測(cè)其脈沖上的毛刺,并判斷有無(wú)毛刺。

2.對(duì)毛刺信號(hào)進(jìn)行計(jì)數(shù)(通過(guò)數(shù)碼管顯示),實(shí)時(shí)上報(bào)毛刺情況(通過(guò)IO輸出)。

3.保證ADC的SNR以及長(zhǎng)時(shí)間寬溫的工作穩(wěn)定性。

毛刺信號(hào)的檢測(cè)算法:

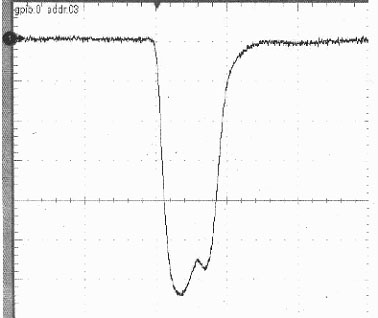

輸出的信號(hào)如下:

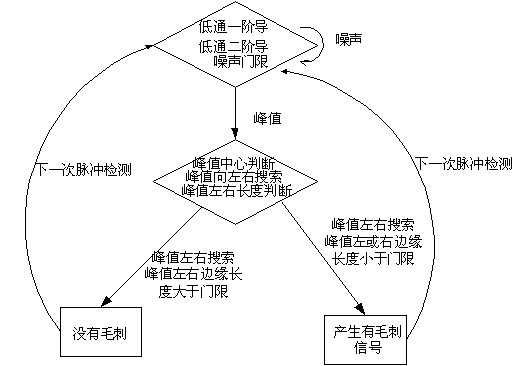

為了準(zhǔn)確檢測(cè)包絡(luò)信號(hào)的毛刺,我們首先檢測(cè)信號(hào)峰值,并判斷信號(hào)峰值的類型,是真正的峰值,還是毛刺的峰值。通過(guò)設(shè)置一定門(mén)限來(lái)區(qū)分毛刺和真正的峰值。

為防止信號(hào)噪聲的干擾,我們引入低通一階導(dǎo)和低通二階導(dǎo)的概念。檢測(cè)流程如下:

其核心算法判斷峰值中心,并同時(shí)向左向右(時(shí)間前后)進(jìn)行邊緣長(zhǎng)度搜索,一單在門(mén)限以內(nèi)還存在另一個(gè)峰值,就可以判斷毛刺的存在。哪怕倆個(gè)峰值相互重合,通過(guò)檢測(cè)峰值邊緣長(zhǎng)度也能判別疊加在峰值上的毛刺。

同時(shí)為了準(zhǔn)確的采集,采集系統(tǒng)的信噪比SNR必須得到保證。影響采集精度的主要要素有以下幾點(diǎn):

量化誤差、Clockjitter和ADCjitter、數(shù)字以及電源干擾

量化精度的提高:

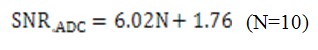

對(duì)于量化誤差對(duì)采集系統(tǒng)的影響,我們?cè)谠撓到y(tǒng)中選用10bit的ADC,理論

Clockjitter的消除:

該方案中采用溫度補(bǔ)償晶體TCXO以及業(yè)內(nèi)頂級(jí)的JittercleaningCLKGenerator芯片來(lái)保證clock的穩(wěn)定性,Clockjitter的消除以及極低的Phasenoise。

在寬溫工作環(huán)境下,普通的晶體隨著工作溫度的變化,晶體的穩(wěn)定度和頻率都會(huì)發(fā)生改變,為解決該問(wèn)題,我們?cè)谠O(shè)計(jì)中選用epson公司的TCXO,該晶體具有業(yè)內(nèi)領(lǐng)先的溫度穩(wěn)定性,在寬溫工作環(huán)境下不會(huì)超過(guò)+/-2ppm,其溫度測(cè)試性能如下:

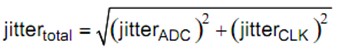

對(duì)于時(shí)鐘芯片的選擇,也是基于同樣的考慮,集成高精度高穩(wěn)定的VCO,具有Jittercleaning功能和clkphaseadj功能。通常,jitter由ADC本身的jitter和CLKjitter組成,各自的RMS再組成總jitter的RMS:

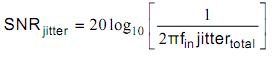

總jitter的RMS會(huì)在采集系統(tǒng)中產(chǎn)生白噪聲,其關(guān)系如下:

采集系統(tǒng)的總和

![]()

采用本時(shí)鐘解決方案,其總的clockjitter在系統(tǒng)中完全能做到<1ps。在忽略信號(hào)noise,DNL等情況下,fin和clockjitter有如下關(guān)系:

系統(tǒng)電源干擾的解決方案:

1.電源抑制(PSR)是采集系統(tǒng)的比較重要的指標(biāo),高的PSR能擬制電源上的CML共模噪聲,該方案中選用的ADC具有80dB以上的電源擬制比。

2.有效的數(shù)字-模擬電源隔離和濾波電路。本方案中采用PICOR的專業(yè)有源EMI濾波器,能在電源上產(chǎn)生65dB的共模制比和80dB的差模擬制比,遠(yuǎn)遠(yuǎn)高于通用的磁珠等EMI濾波效果。

3.合理的PCB布線和接地

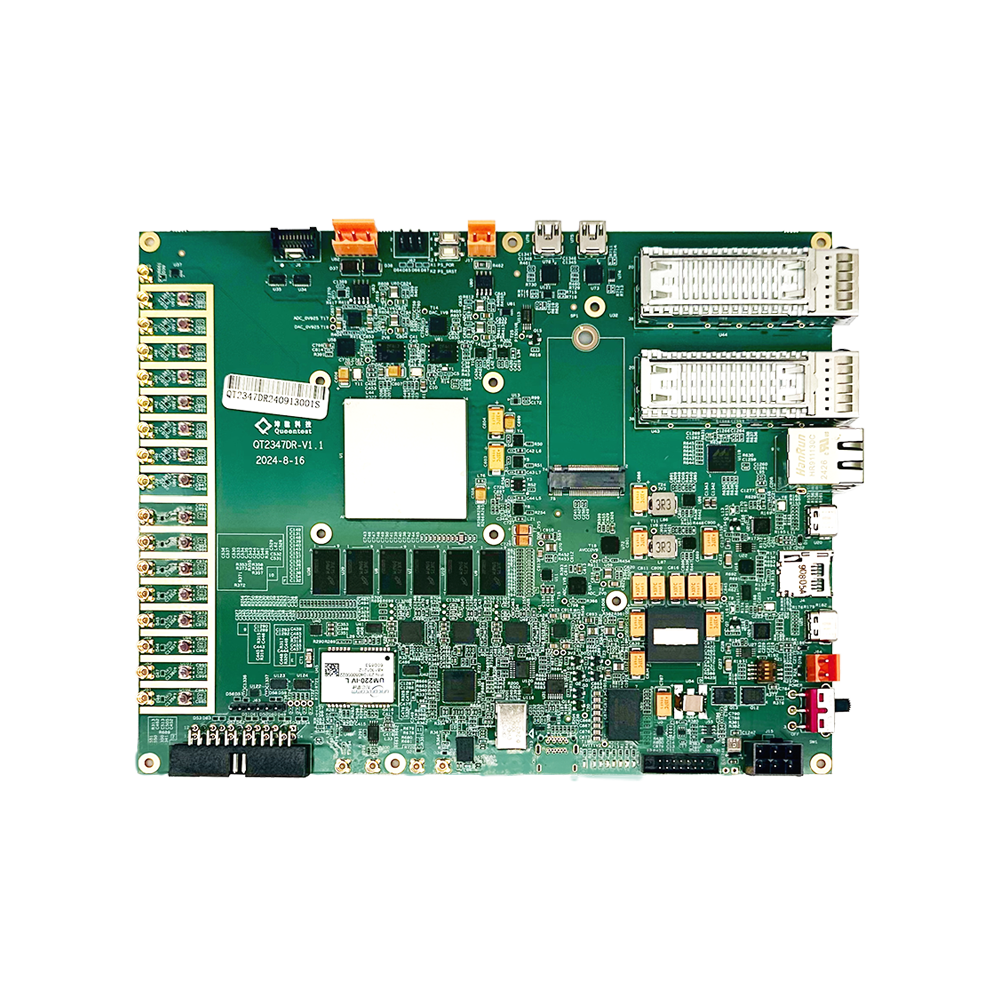

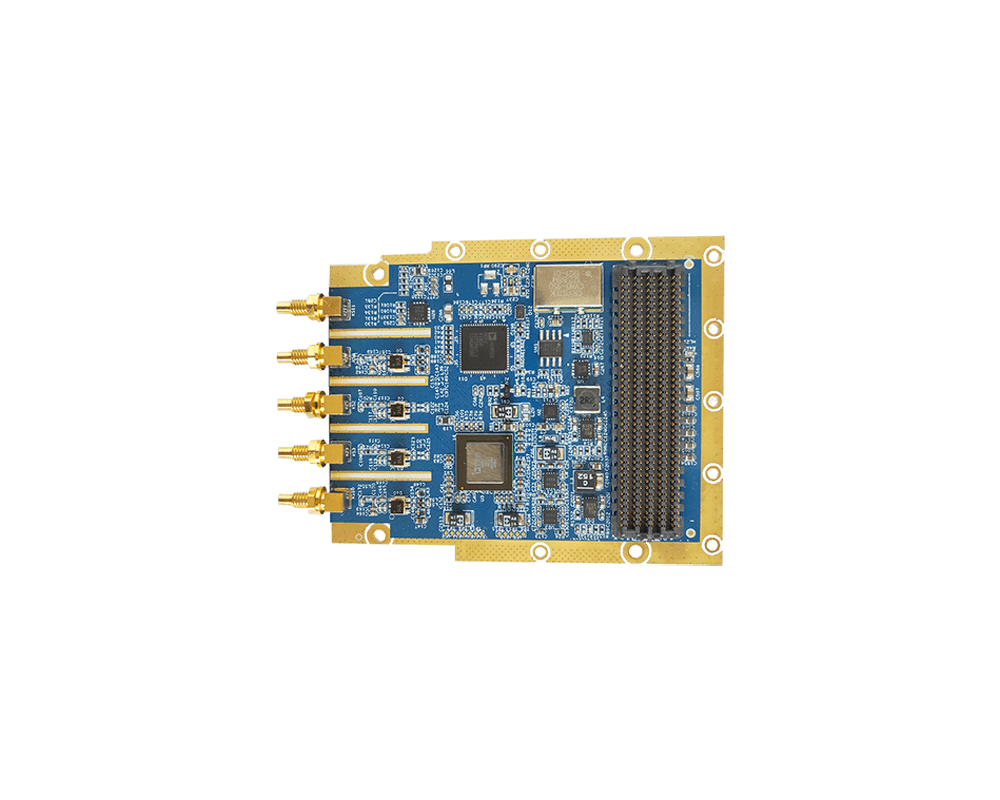

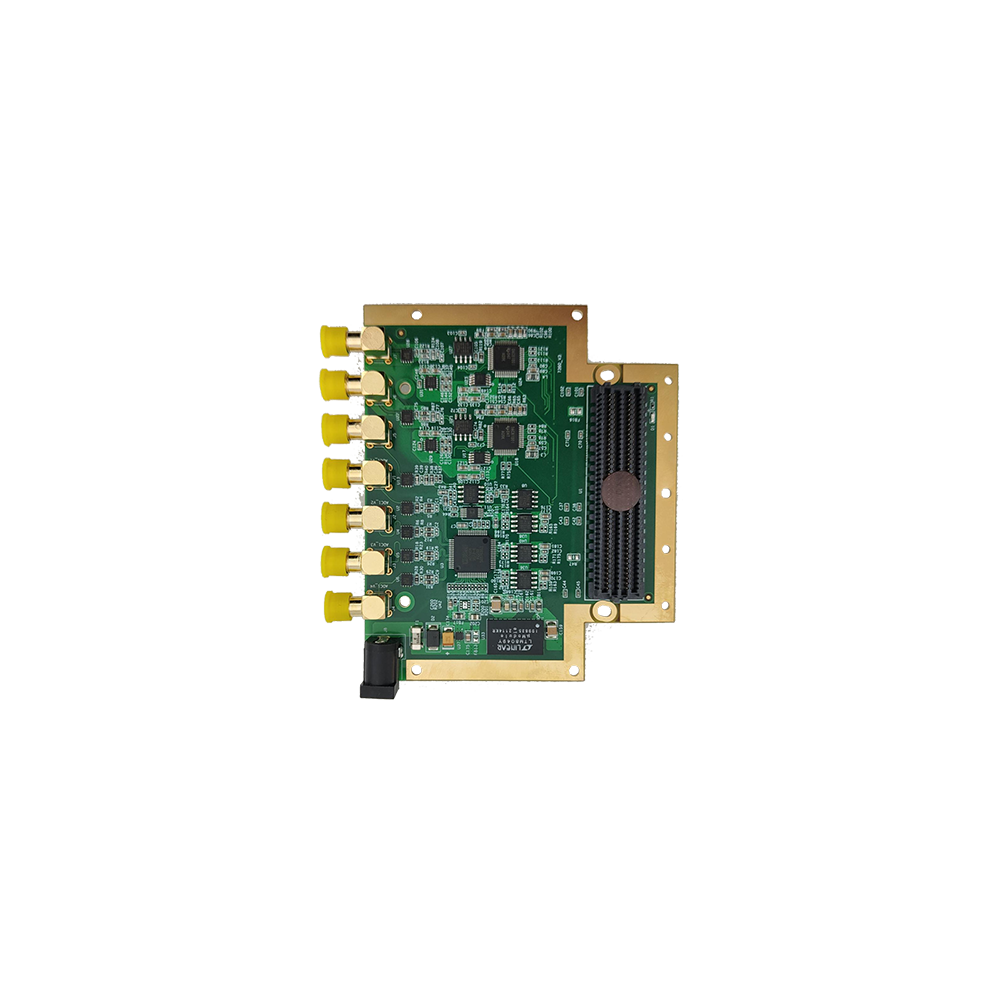

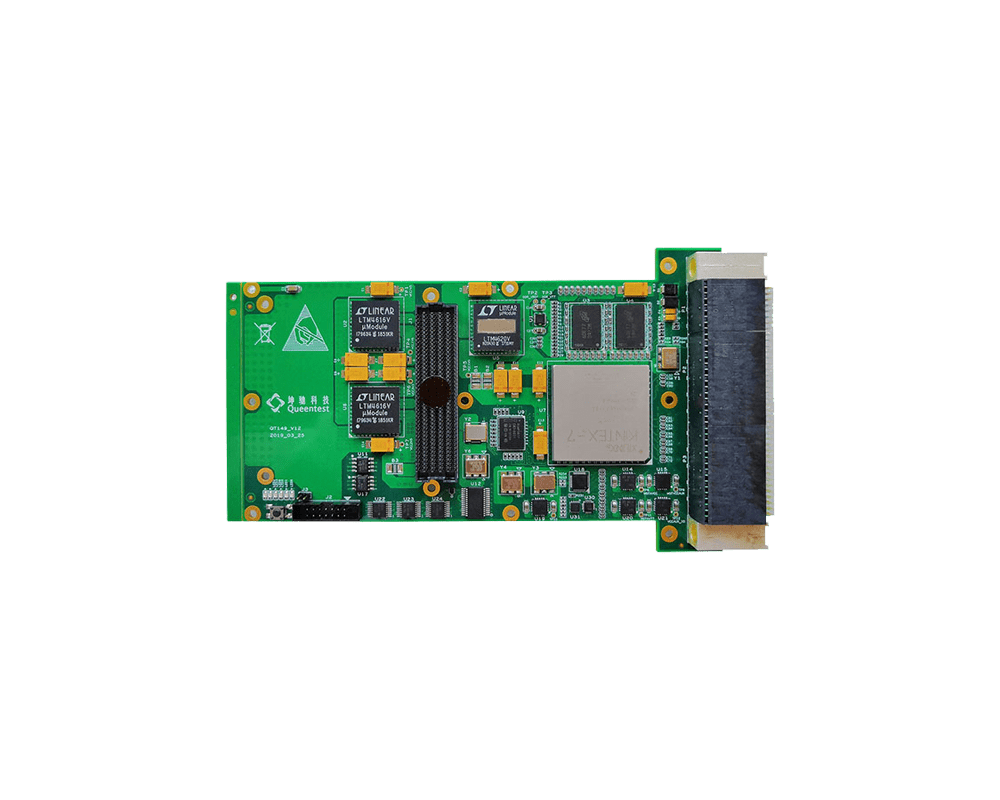

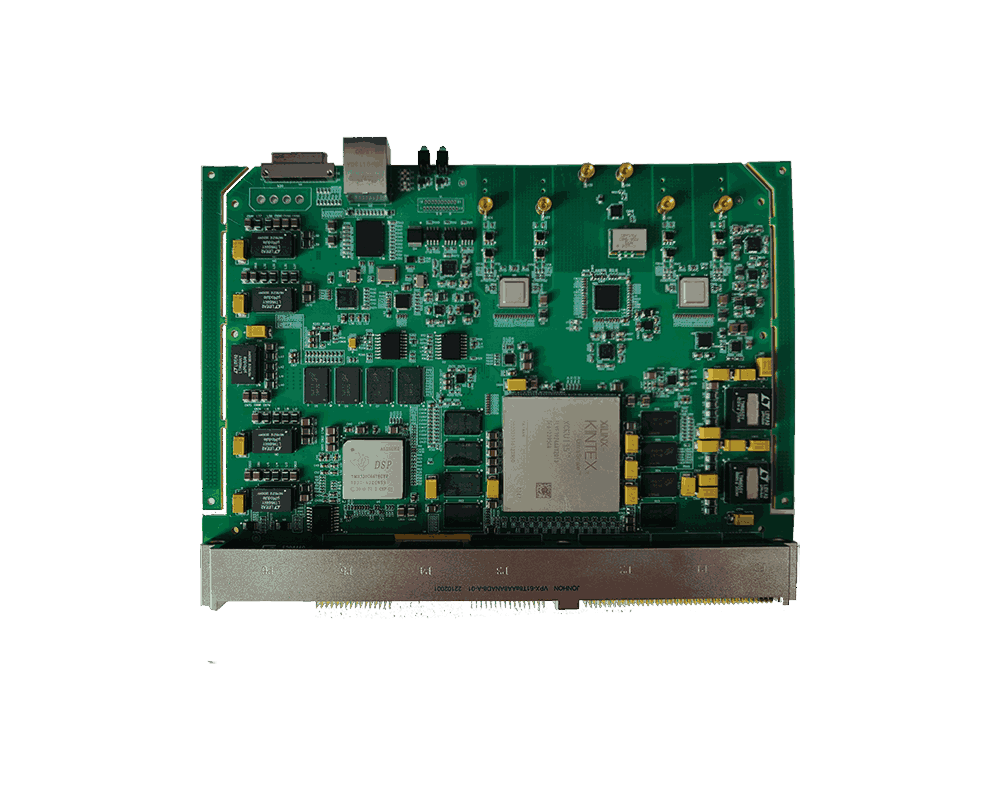

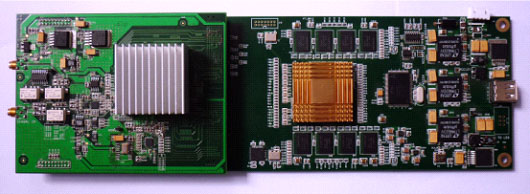

板卡實(shí)物圖:

-

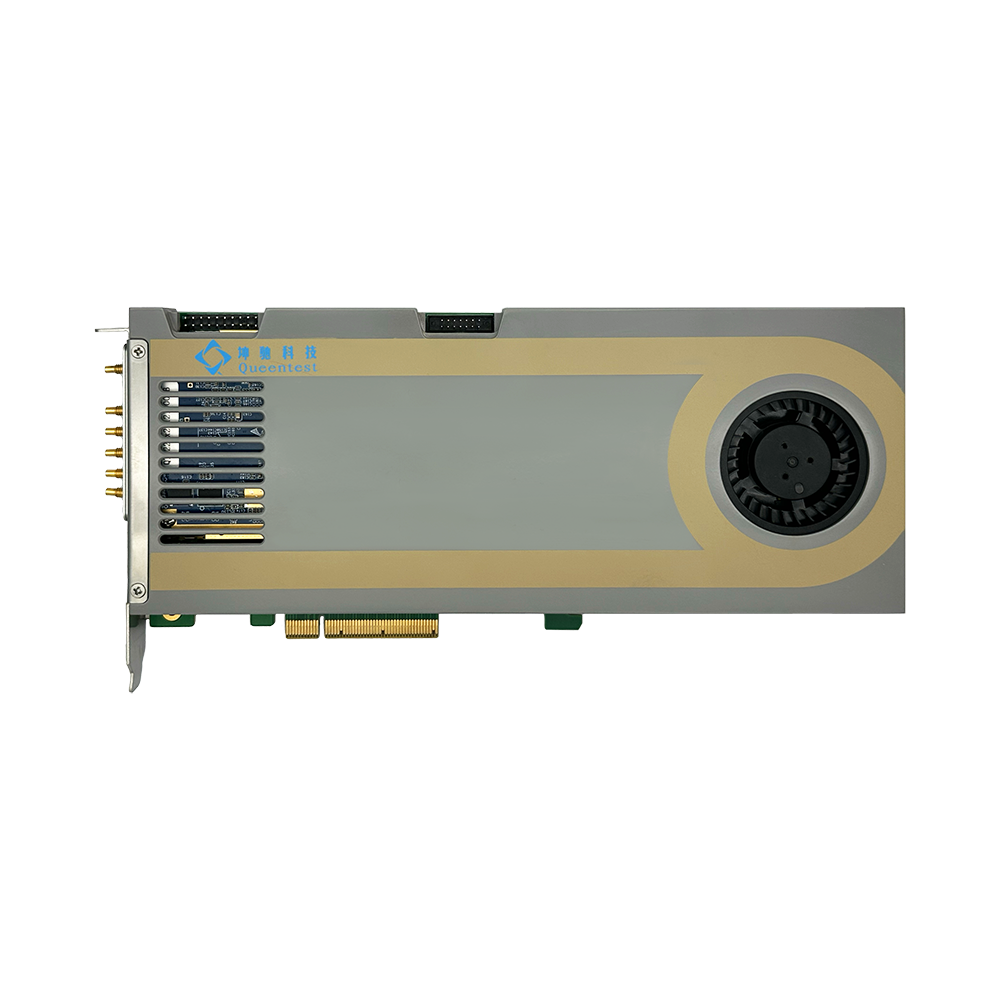

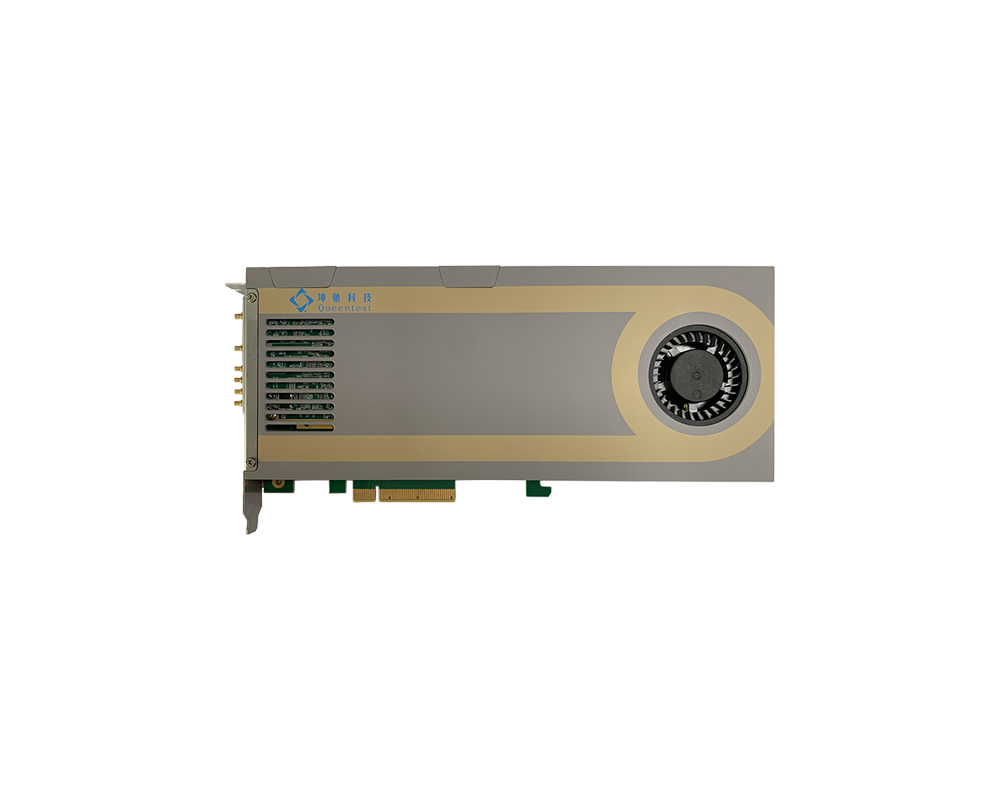

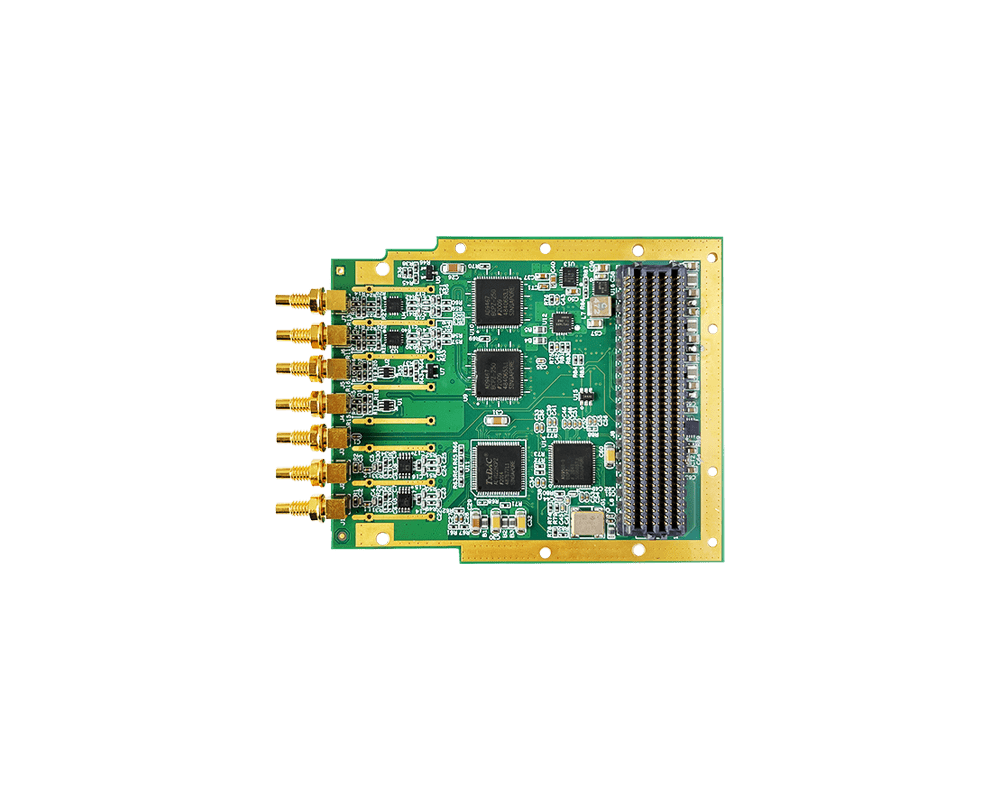

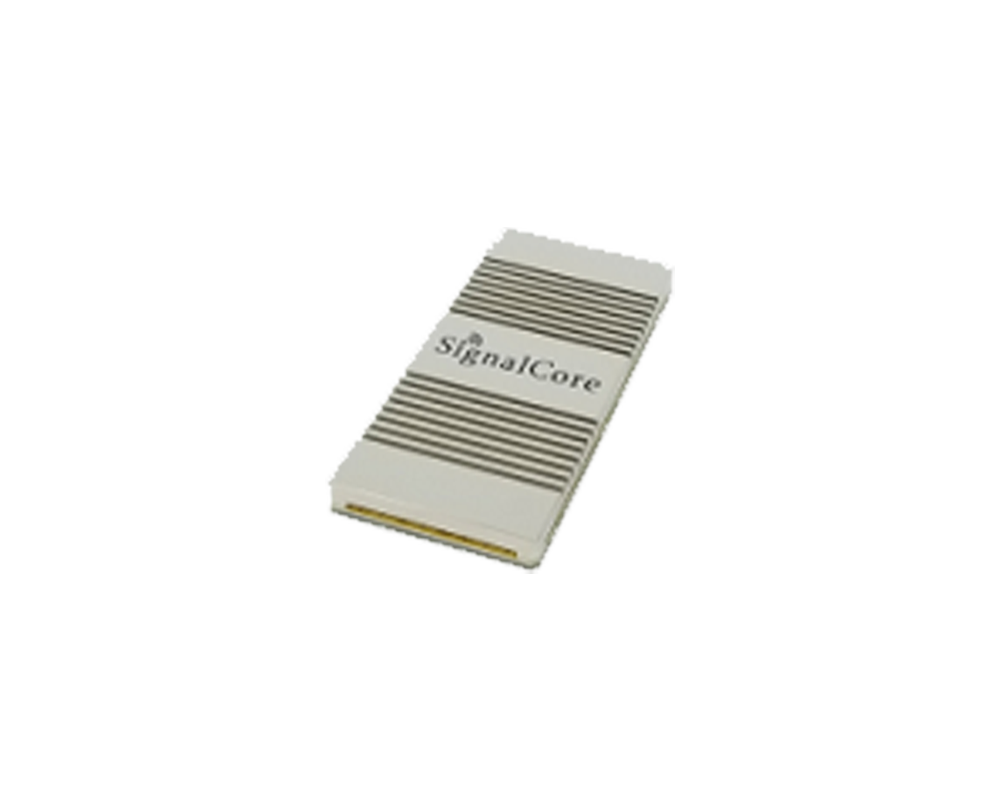

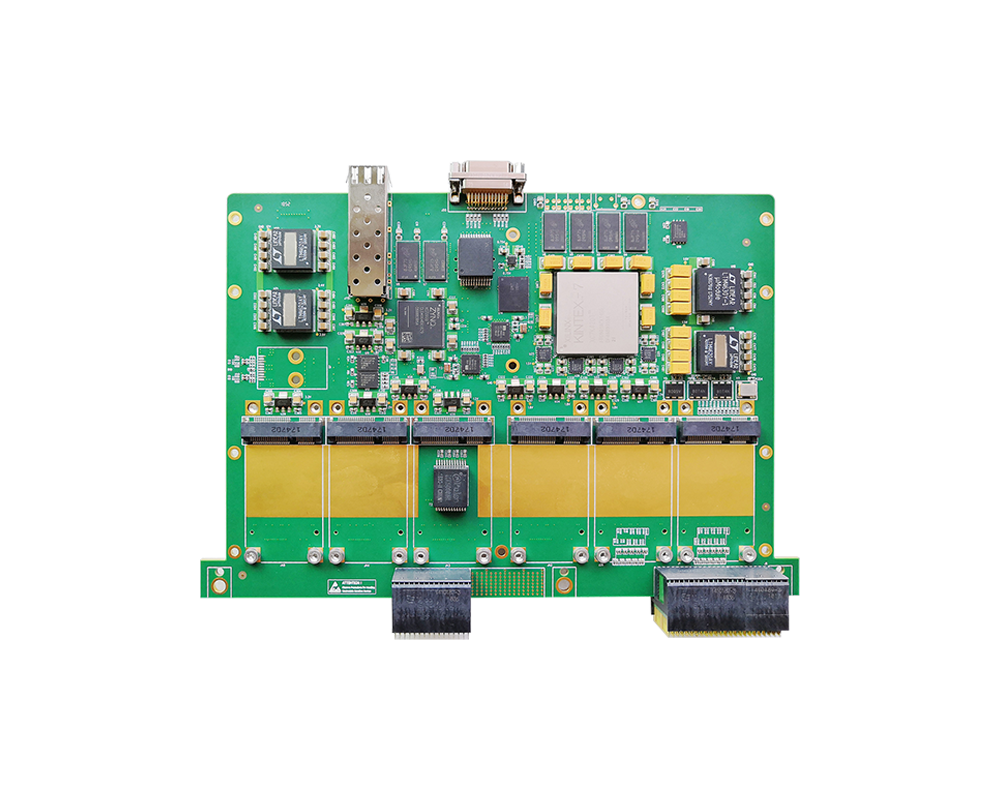

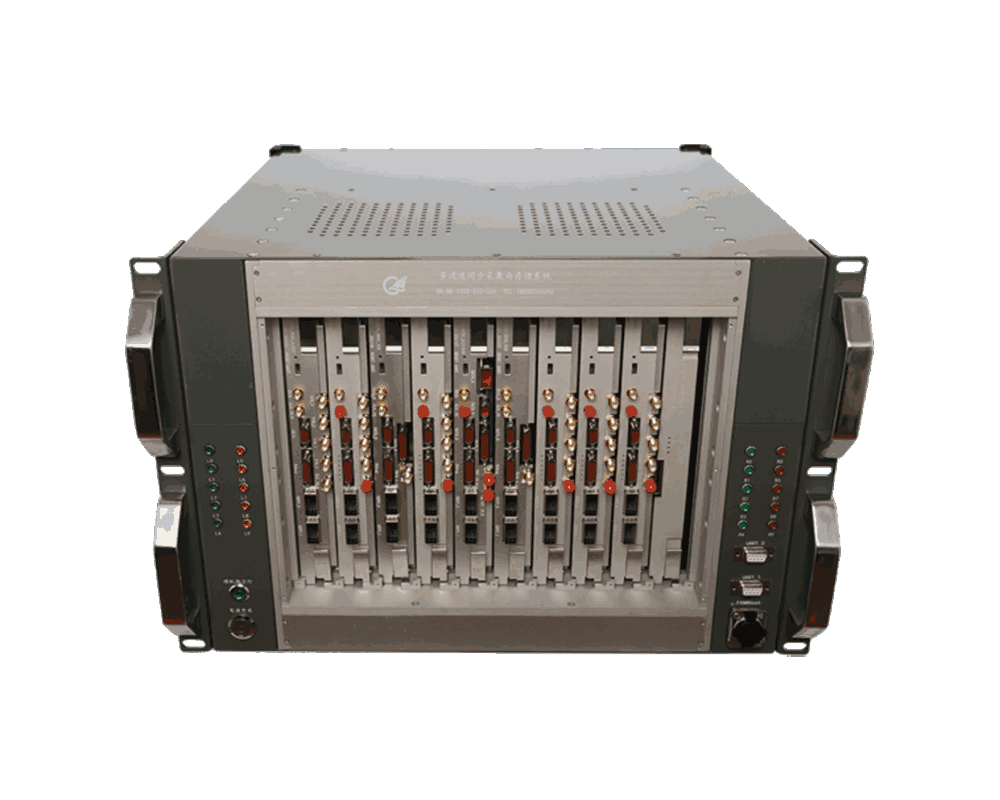

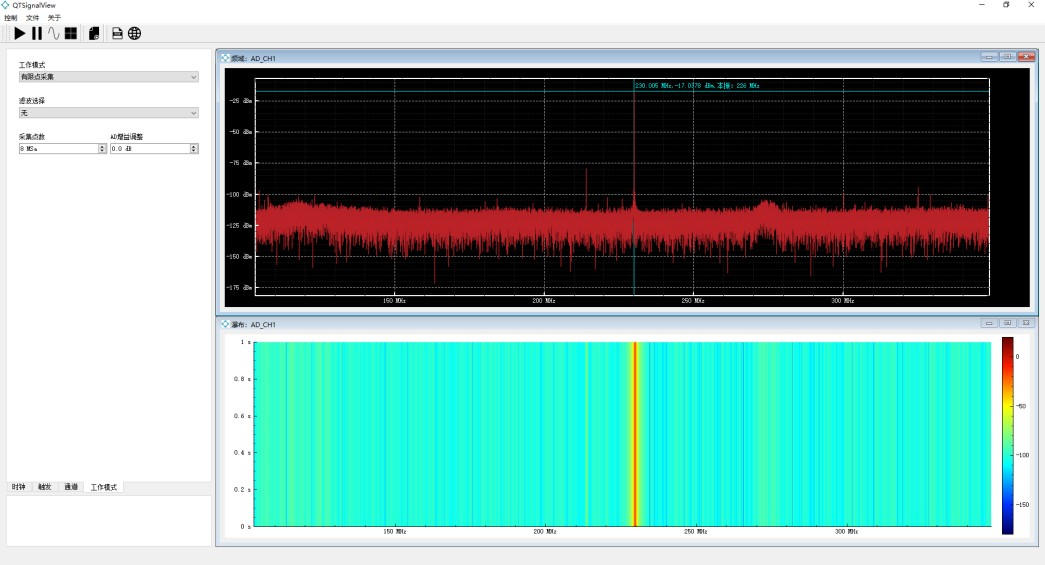

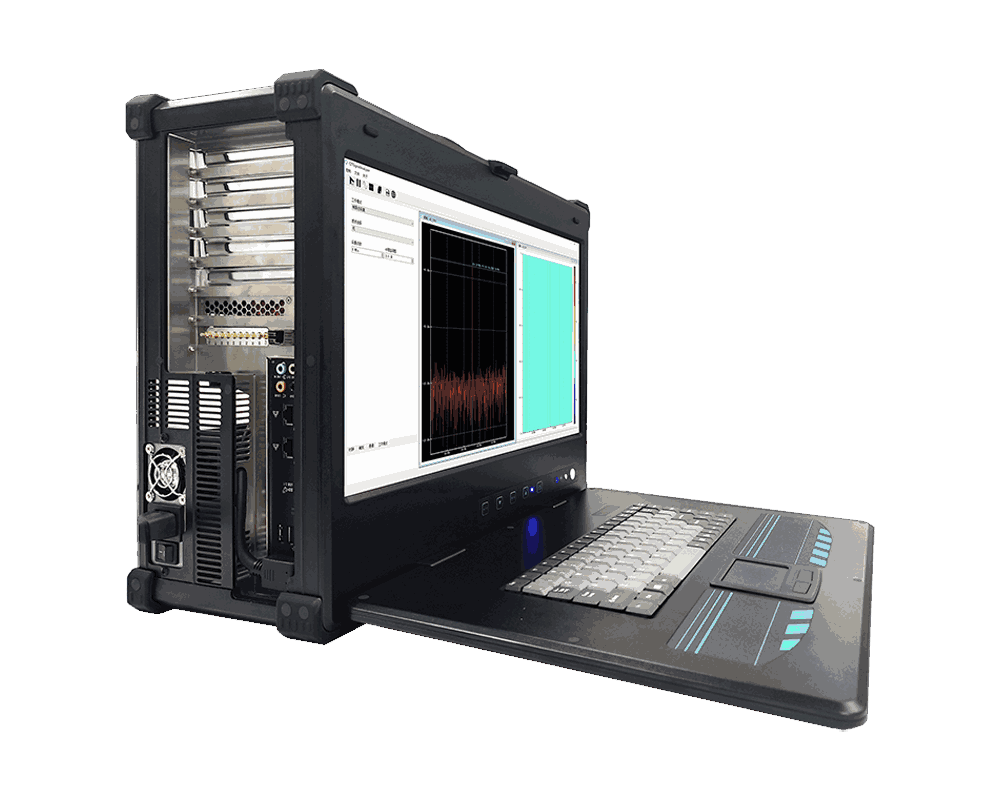

QTS12509RF-射頻采集存儲(chǔ)系統(tǒng)

收發(fā)信號(hào)頻率范圍75MHz~6GHz 支持2KHz~200MHz不同帶寬的信號(hào)實(shí)時(shí)記錄 2GB/s持續(xù)流盤(pán)速率

-

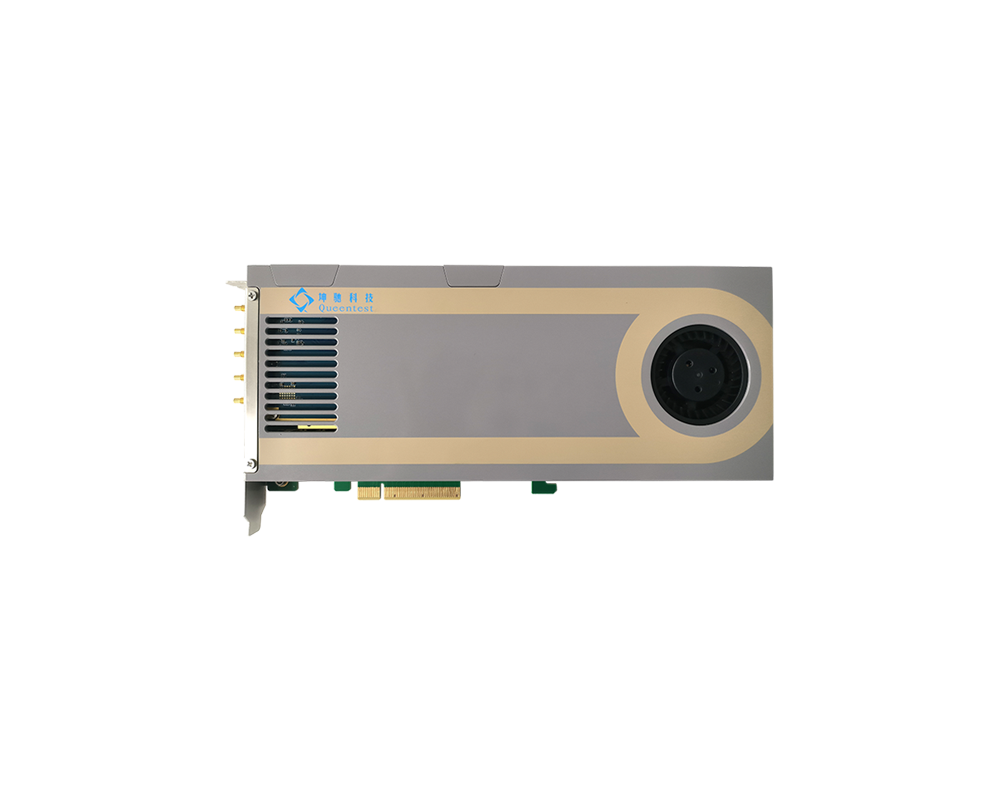

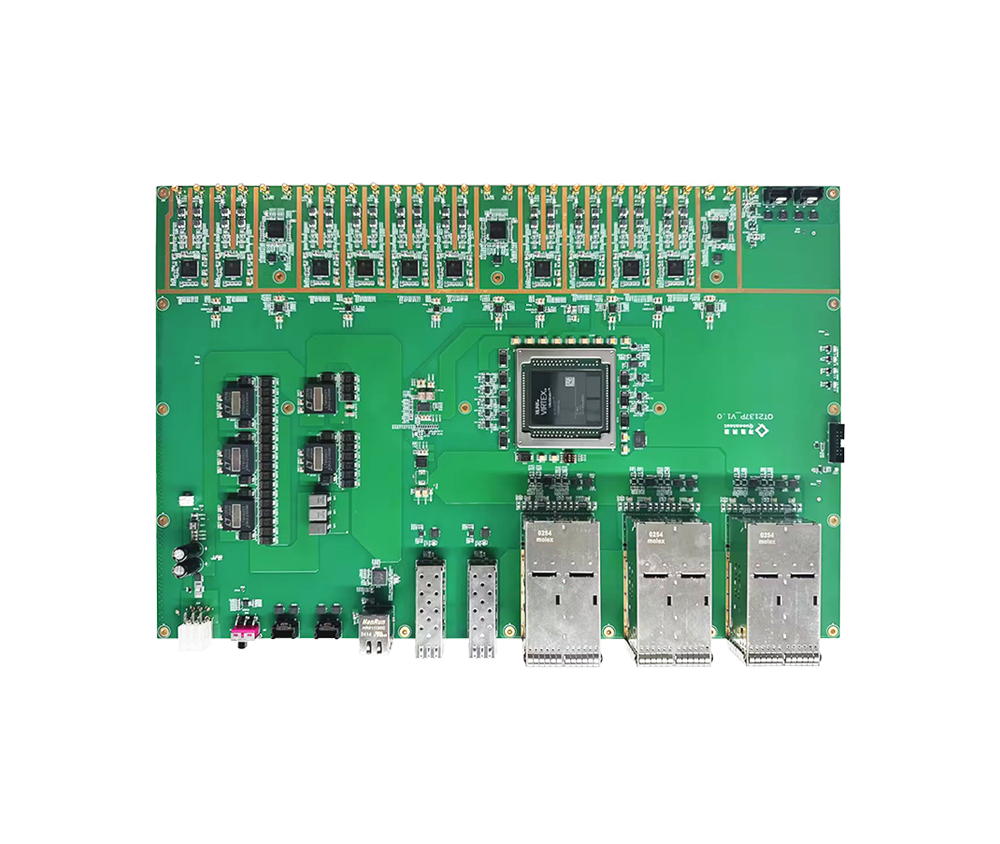

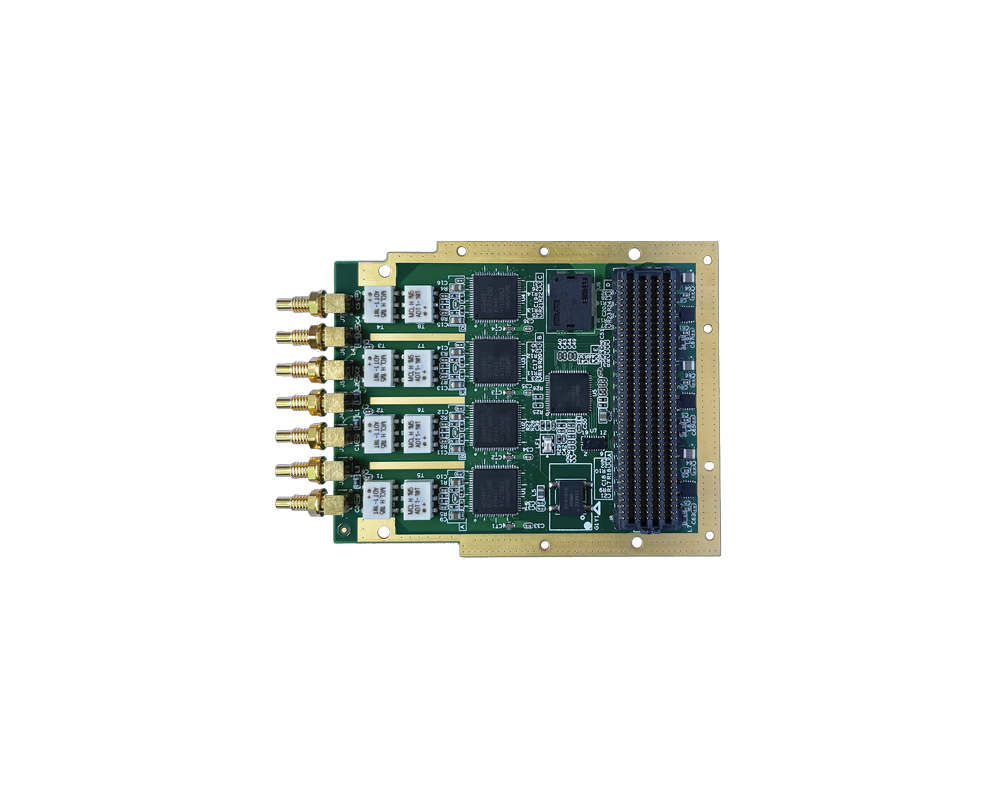

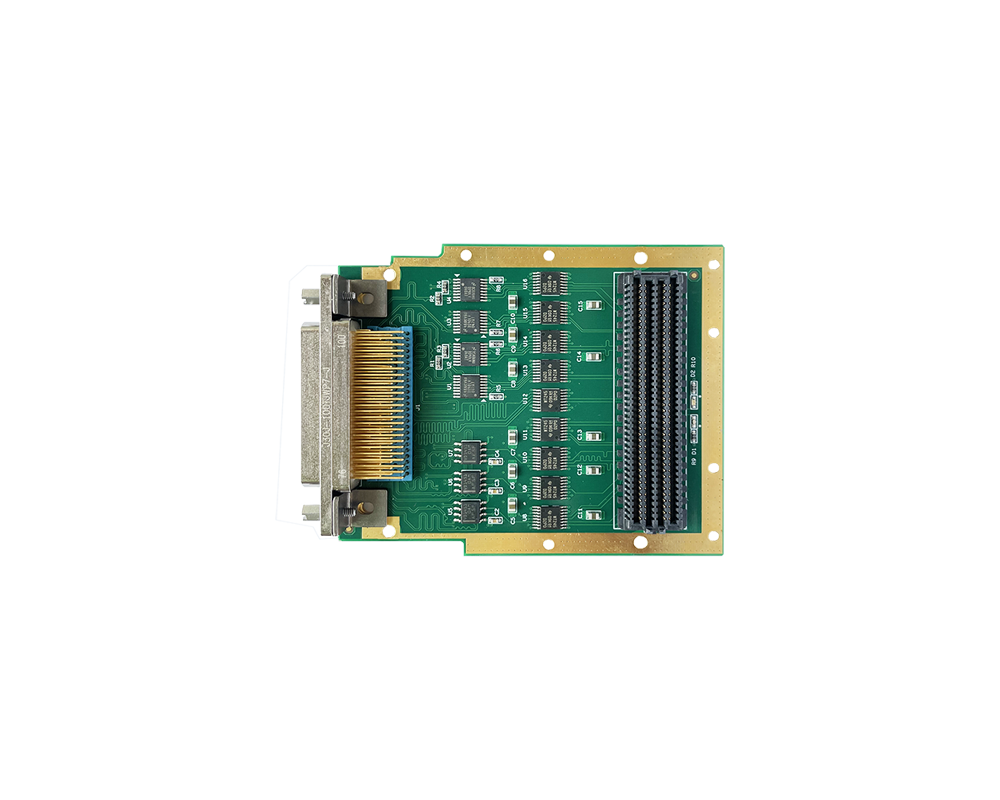

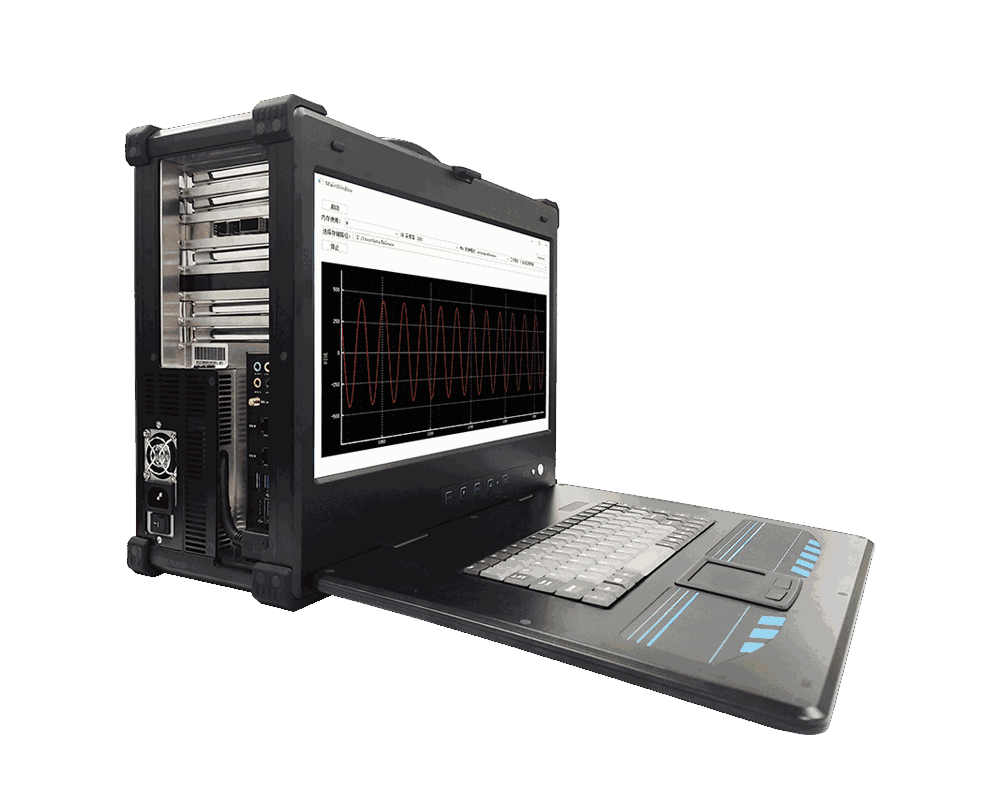

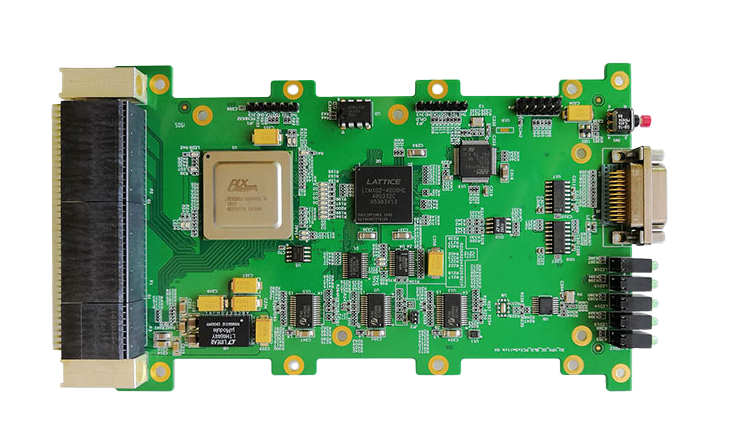

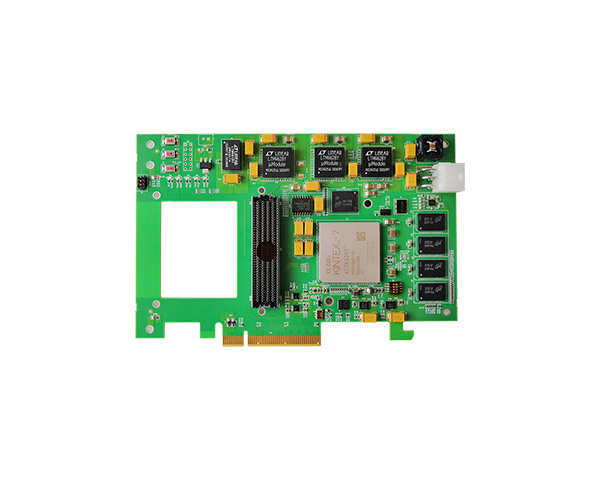

QT7010-PCIe載板

K7 325T PCIe2.0x8 FMC FPGA載板

-

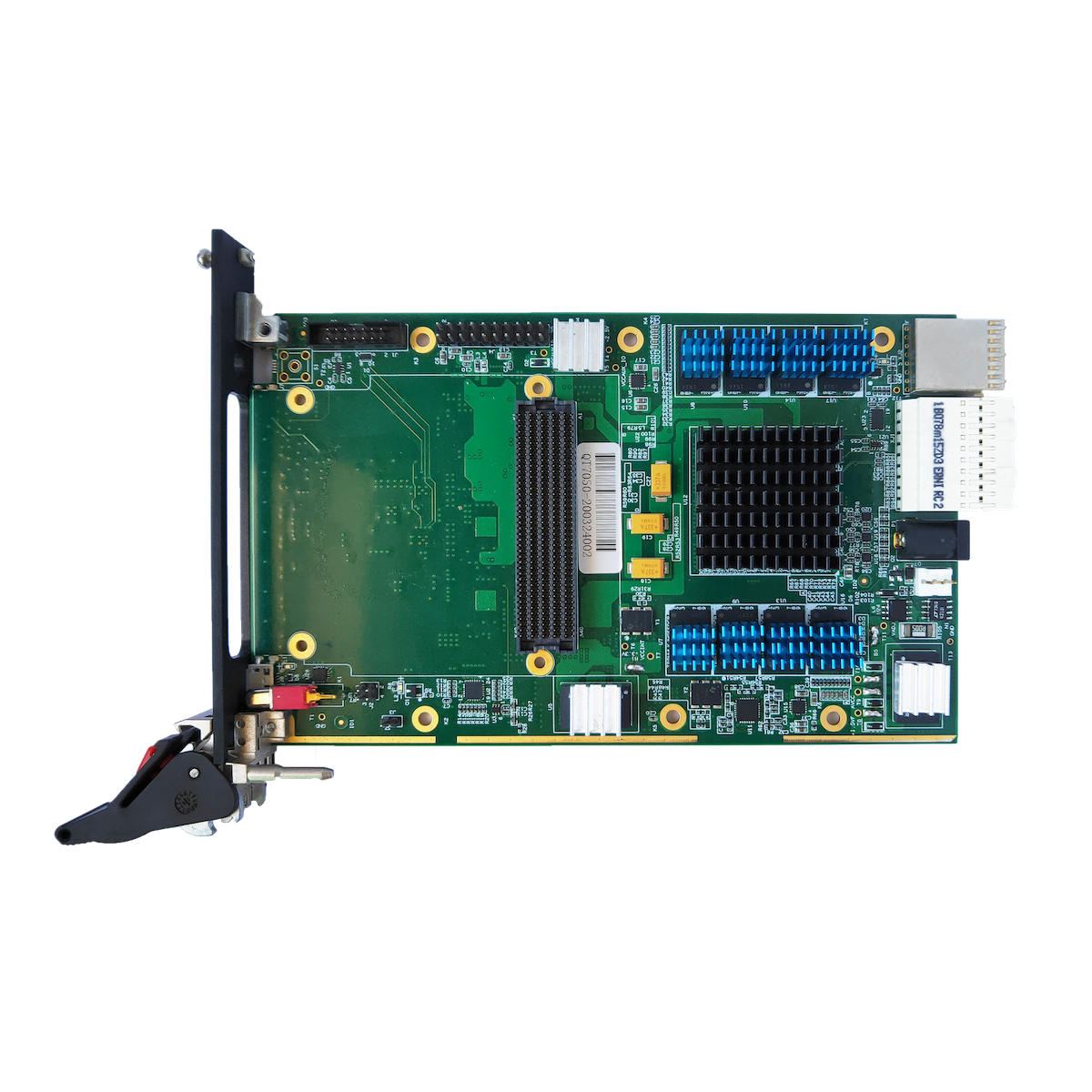

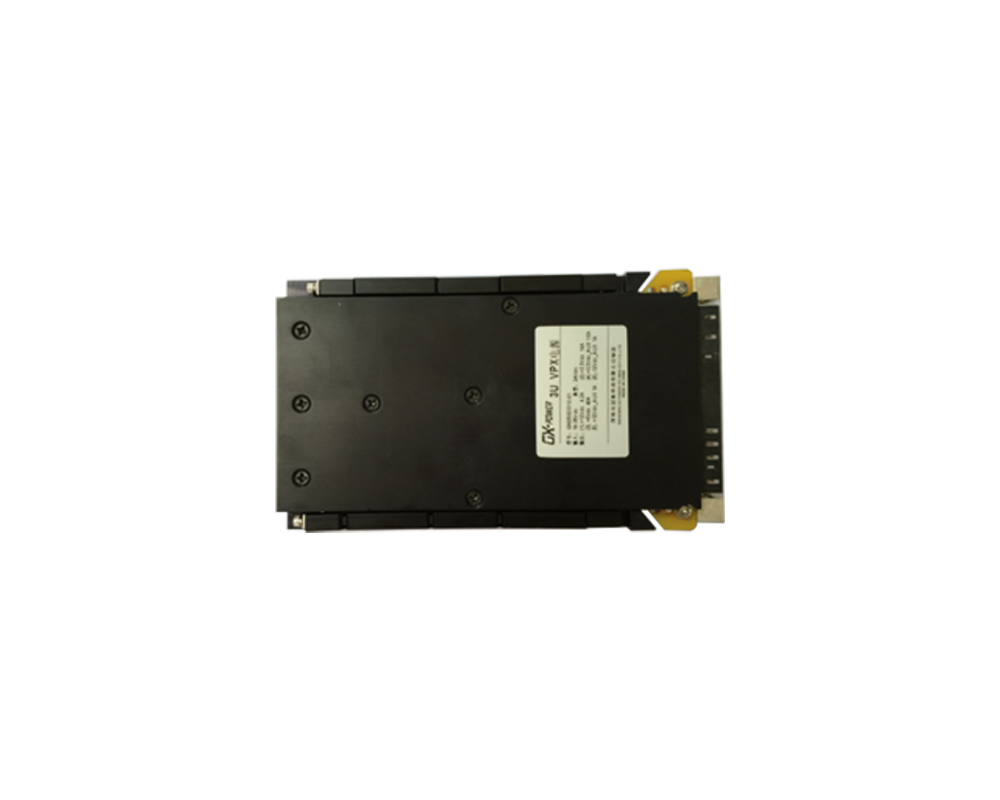

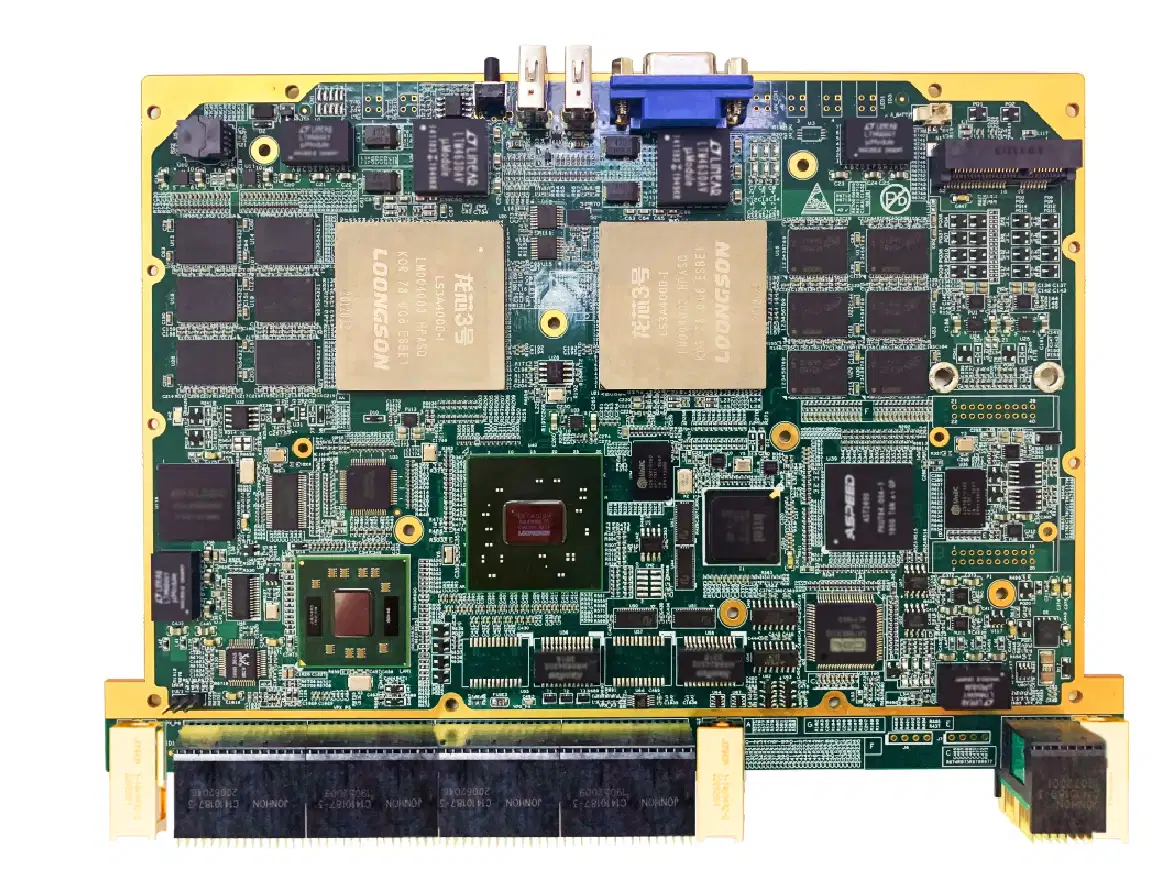

VPX-LX642

坤馳科技VPX-LX642是一款雙3A5000處理器的VPX主控板,遵循6U VPX標(biāo)準(zhǔn),板卡PCB支持軍用加固結(jié)構(gòu),主要應(yīng)用于航空航天、車載、艦載等惡劣環(huán)境...

-

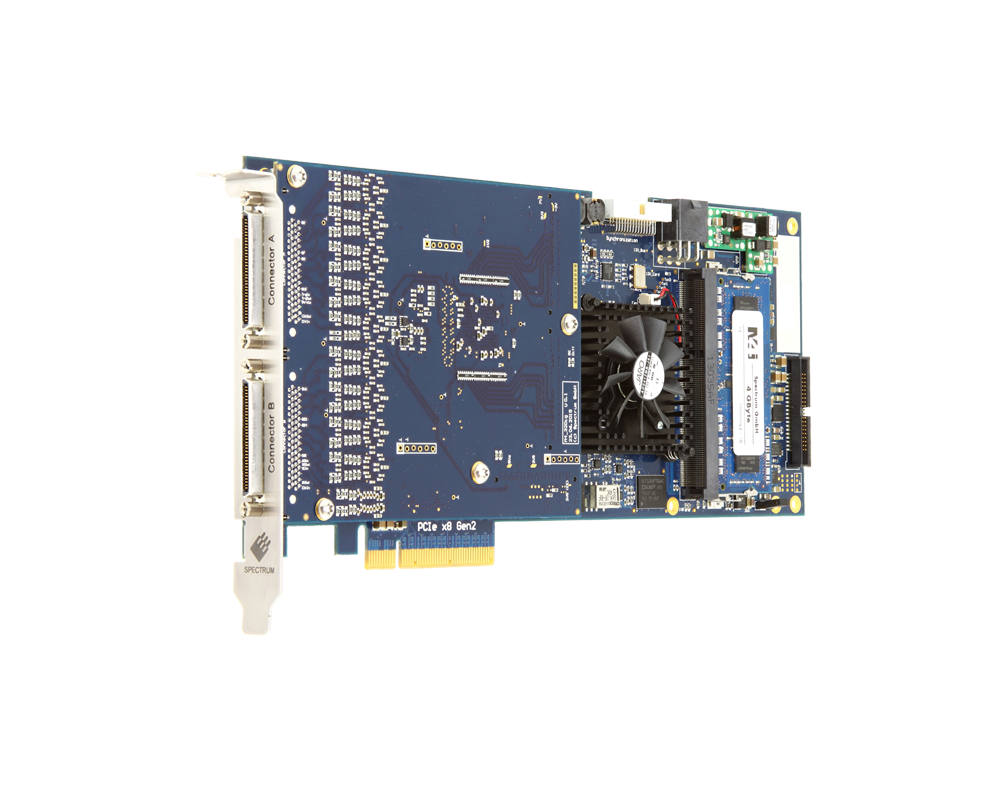

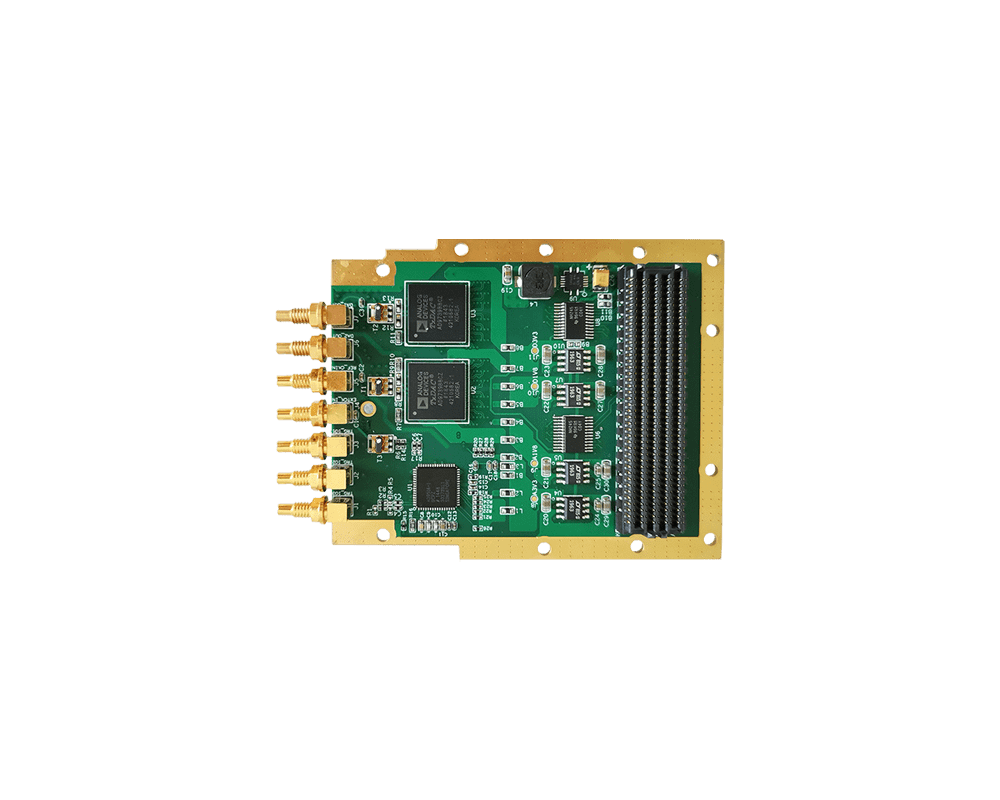

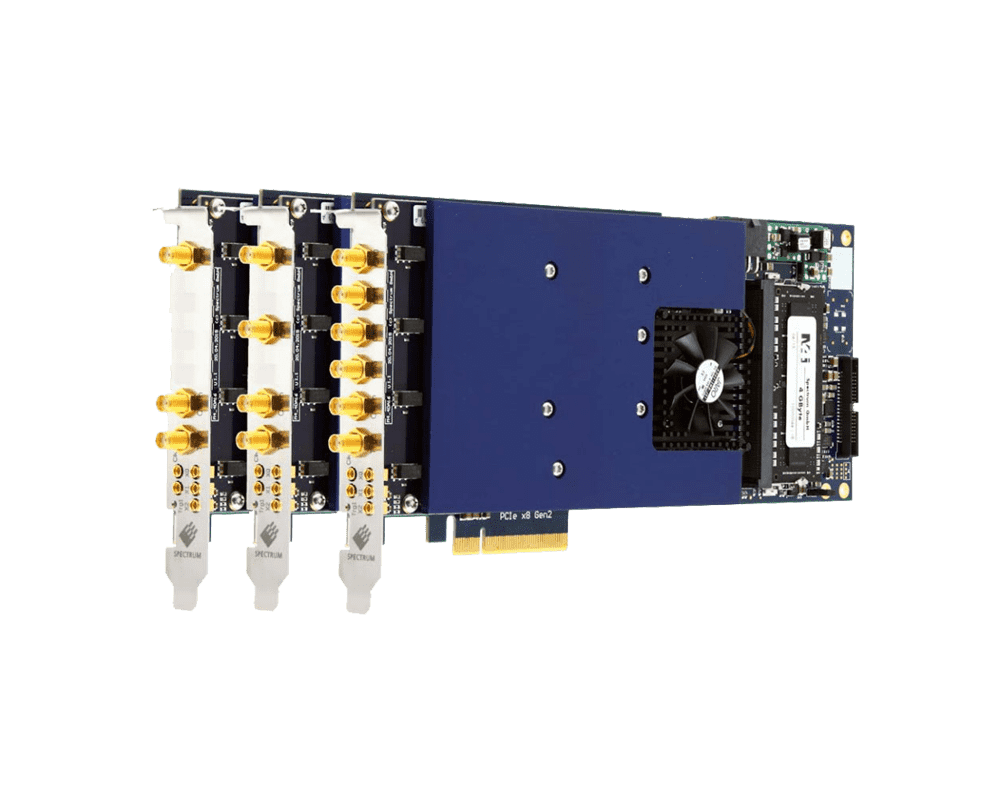

m4i.66xx-x8系列

高625 MS/s 4通道和1.25GS/s 2通道 快速16bit任意波形產(chǎn)生