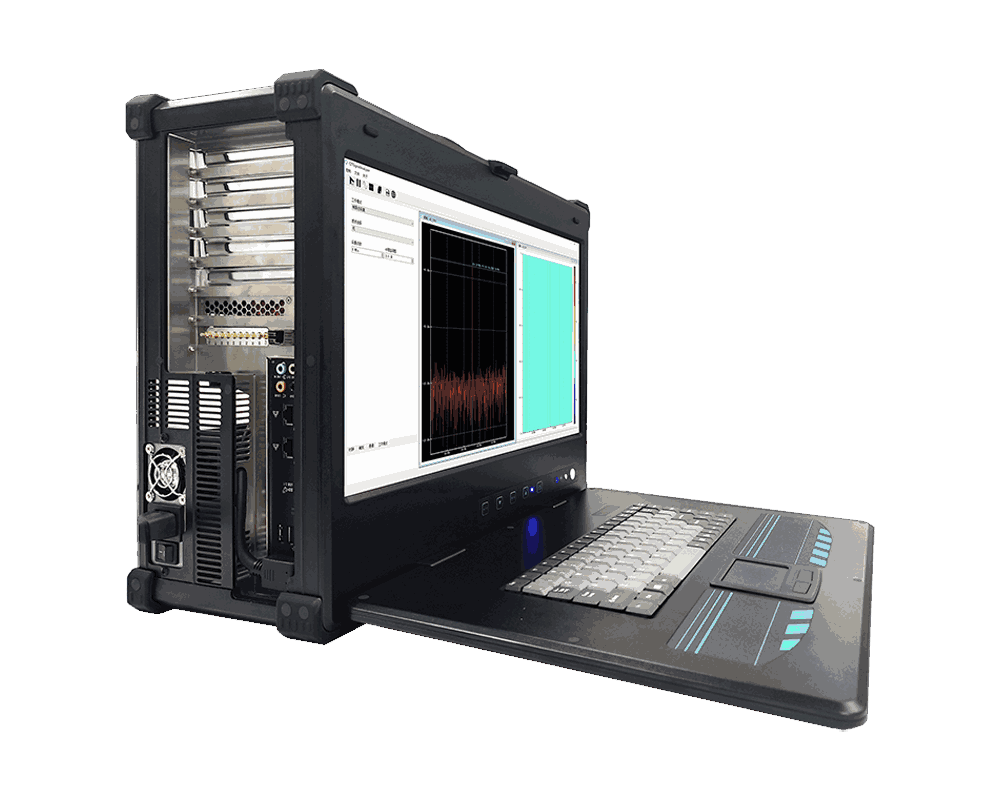

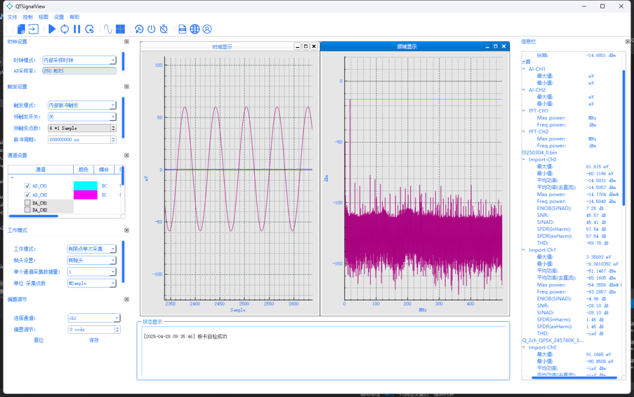

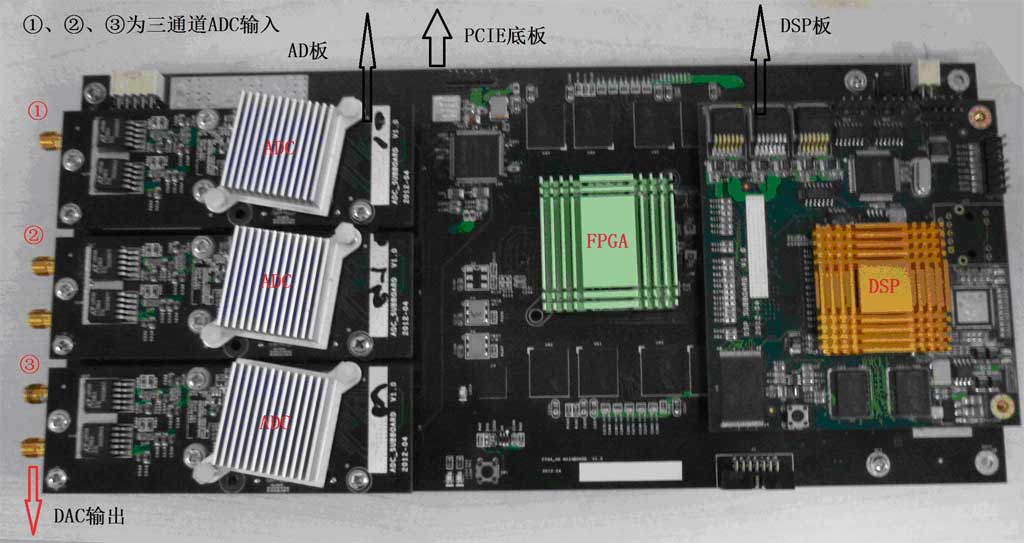

激光雷達三通道高速信號采集系統

激光雷達數據采集卡在數據采集系統 中的應用,詳情如下:

一、采集系統規格

1.3通道,10bit1GSPSADC轉換器

2.模擬帶寬100MHz

3.輸入方式:單端

4.輸入阻抗50Ω

5.ENOB:9.1bits@500MHz

6.非線性失真±0.25LSB

7.SNR:44dB

8.存儲:板載1GDDR2

9.信號調理模塊,支持PGA和AGC功能

10.大規模FPGA,支持數字信號實時處理,包括三通道FFT

11.低抖動采集時鐘發生器

12.TI320C6455DSP模塊

13.RS232和RS422通信接口

14.板卡尺寸:284mm*130mm

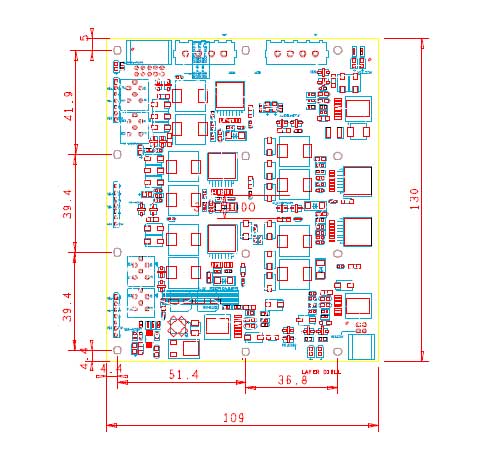

15.外供電電源板尺寸圖如下(單位:mm):

二、FPGA控制邏輯以及算法實現

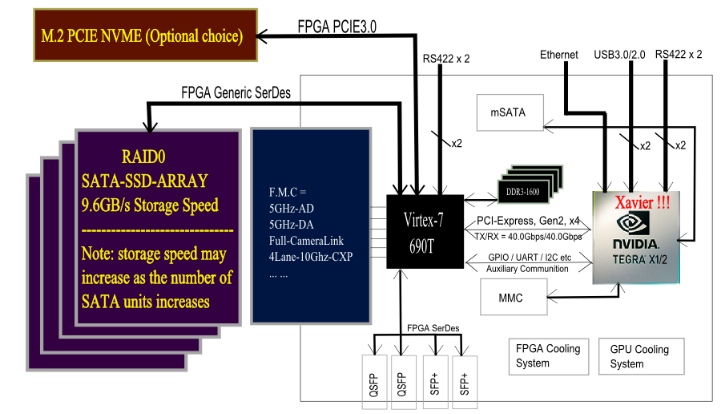

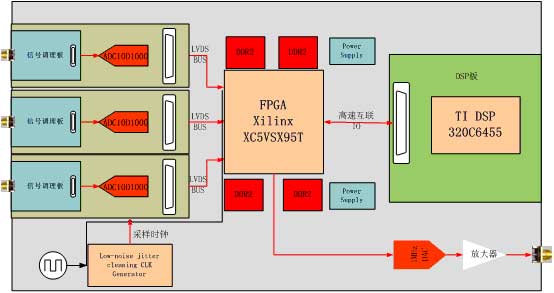

2.1系統組成結構如下:

2.2FPGA部分邏輯實現要求:

①三通道ADCADC10D1000接口設計;

②采樣時鐘配置32bitSPI接口;

③同DSP的通信接口。

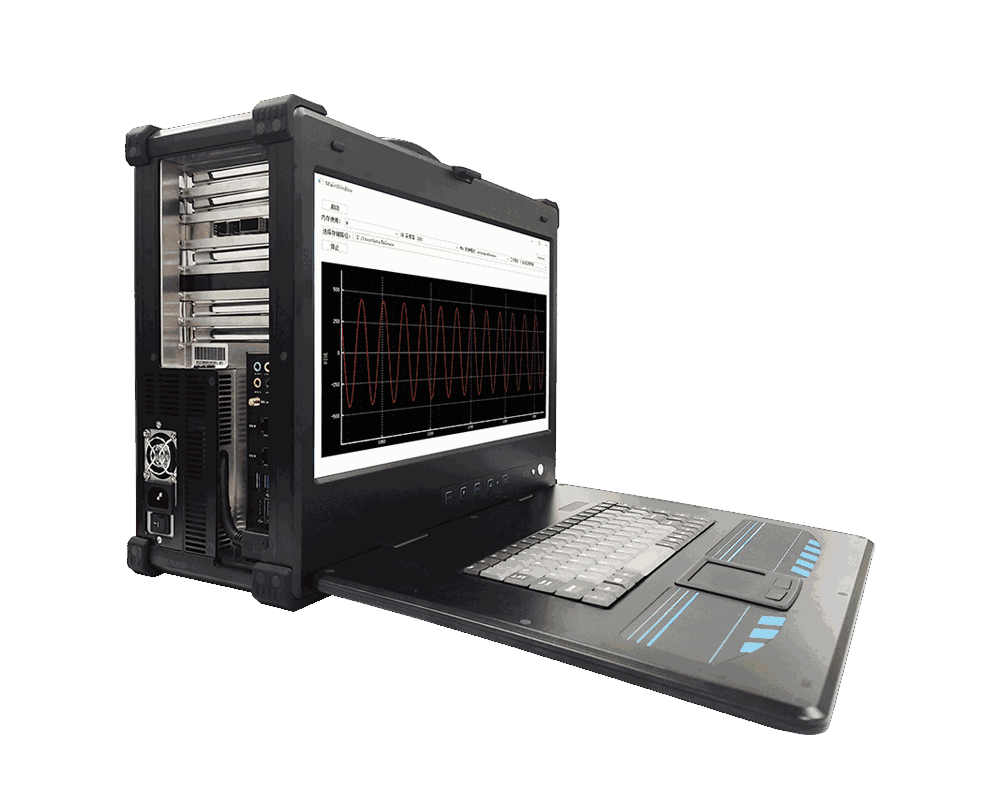

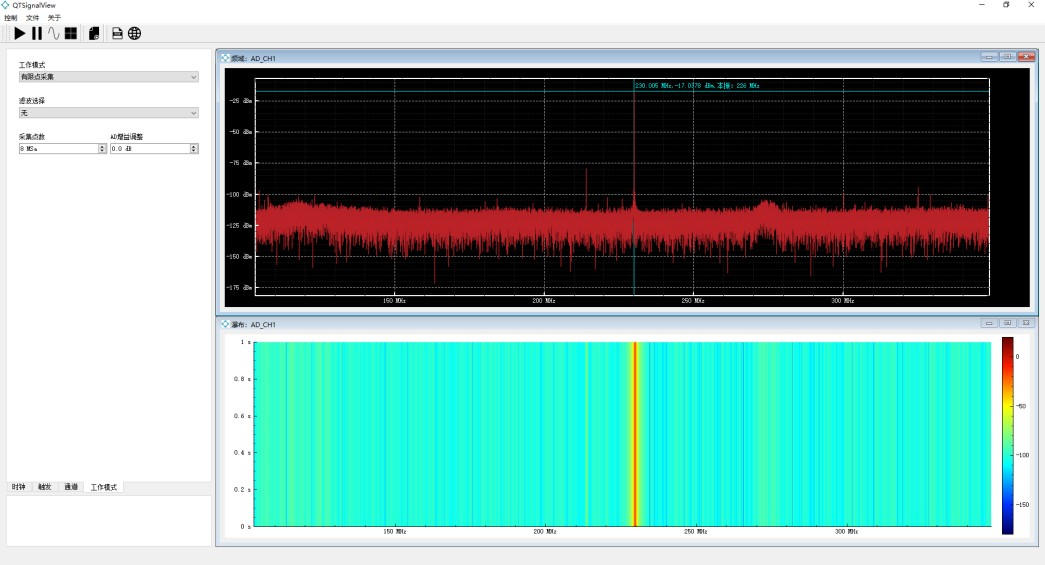

2.3FPGA算法實現:

2.3.1實時波形產生:

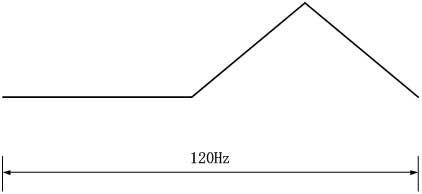

連續產生如下波形

幅度有DAC硬件放大。

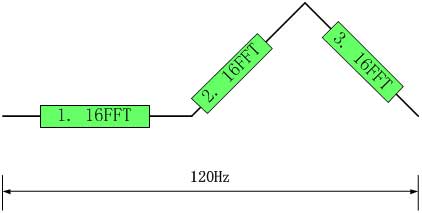

2.3.2在120Hz周期內完成3次16K點的FFT處理(由外部觸發信號給出FFT的起始位置)

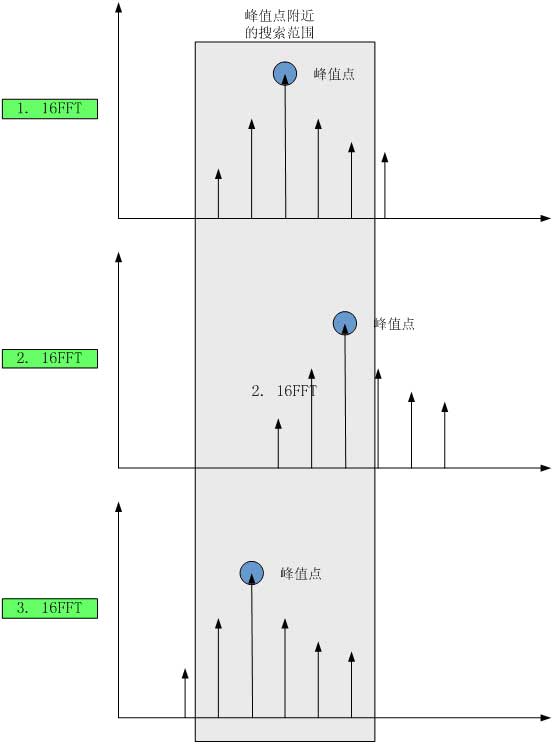

2.3.3FFT部分

①找出1次FFT的峰值點,并在峰值點頻率附近設置搜索范圍;

②在搜索范圍內找到2次FFT以及3次FFT的峰值;

③將三次峰值點記錄并上傳到DSP;

④XilinxXC5VSX95T具備的FFT能力如下:

16bit數據輸入,32k點FFT,工作時鐘250MHz,需要資源為,LUT3300個,乘法單元9個,延遲約400us。所以,我們按照3通道500M/s,每秒計算360次,間隔約2.7ms,所以當前的FPGA完全支持3通道32kFFT實時計算。此時輸出運算結果數據量為2(實部虛部)x2(16bit)X32K。

2.3.4AGC部分

由于ADC輸出信號大小不一定,我們在硬件上設計了數字PGA電路,通過SPI總線控制增益。每次需要計算輸入信號功率,通過濾波后,根據功率設置動態調整增益大小。

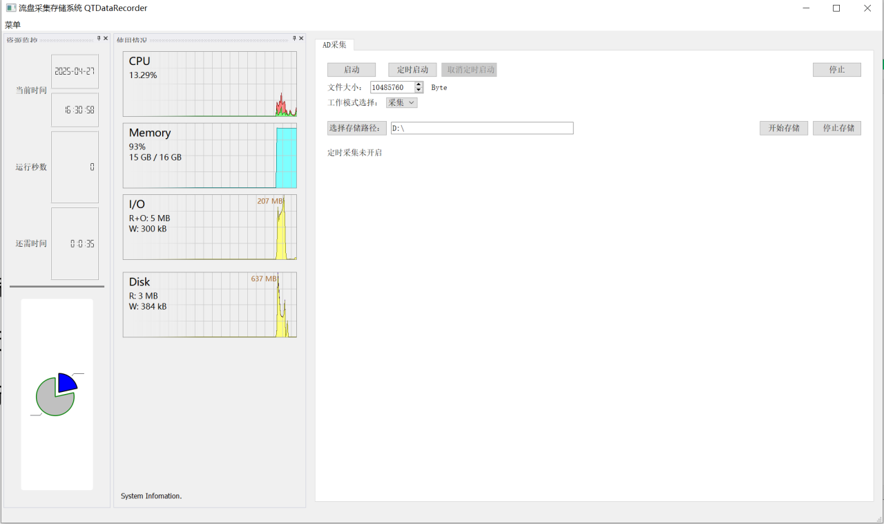

2.3.5DSP硬件部分

設計基于TI320C6455芯片設計DSP板的硬件電路;包括原理圖和PCB設計以及調試。DSP主要功能,同FPGA接口,按主板已經定義的接口和大小設計PCB。兩個RS232接口,兩個RS485接口。

2.3.6DSP軟件部分部分

①通過接受RS485接口接收主機命令,通過串口發送命令。

②接收FPGA輸出的峰值數據信息。

③控制系統電源管理。

-

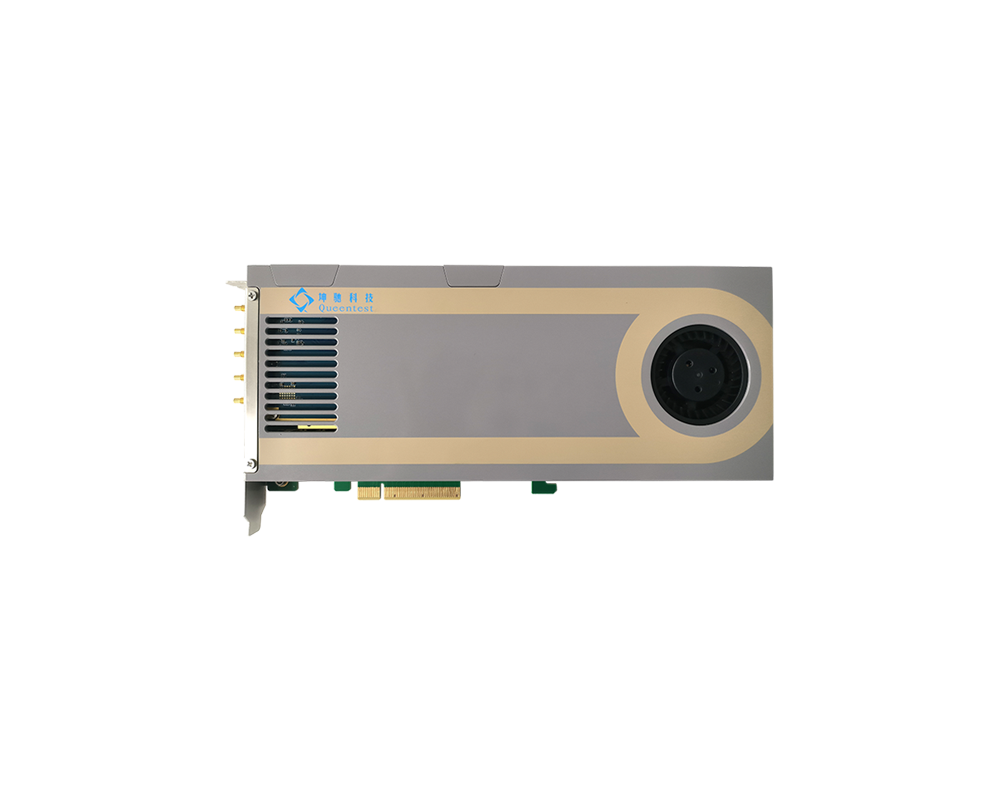

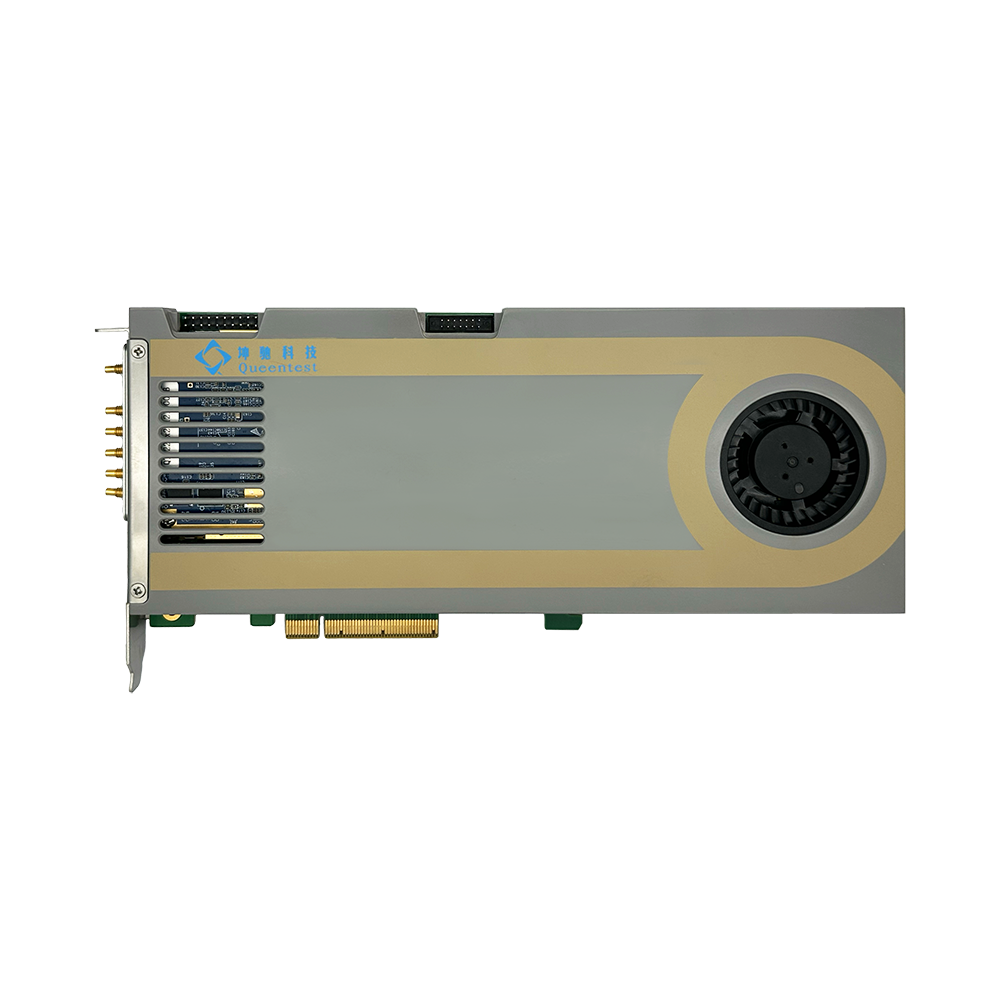

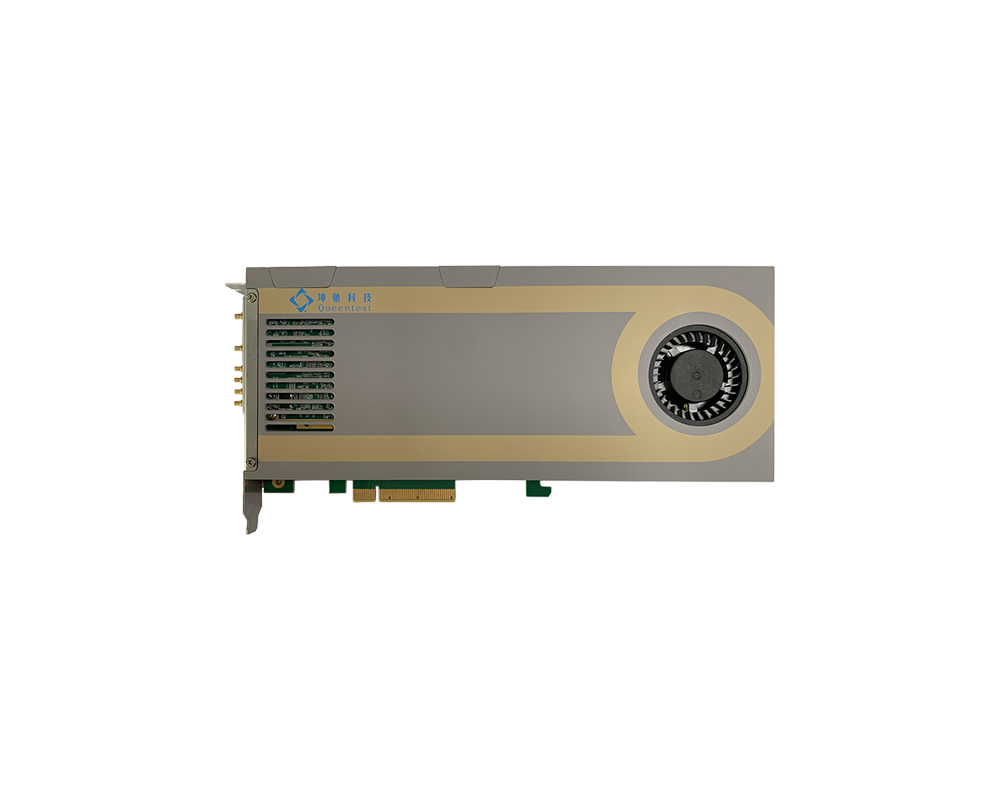

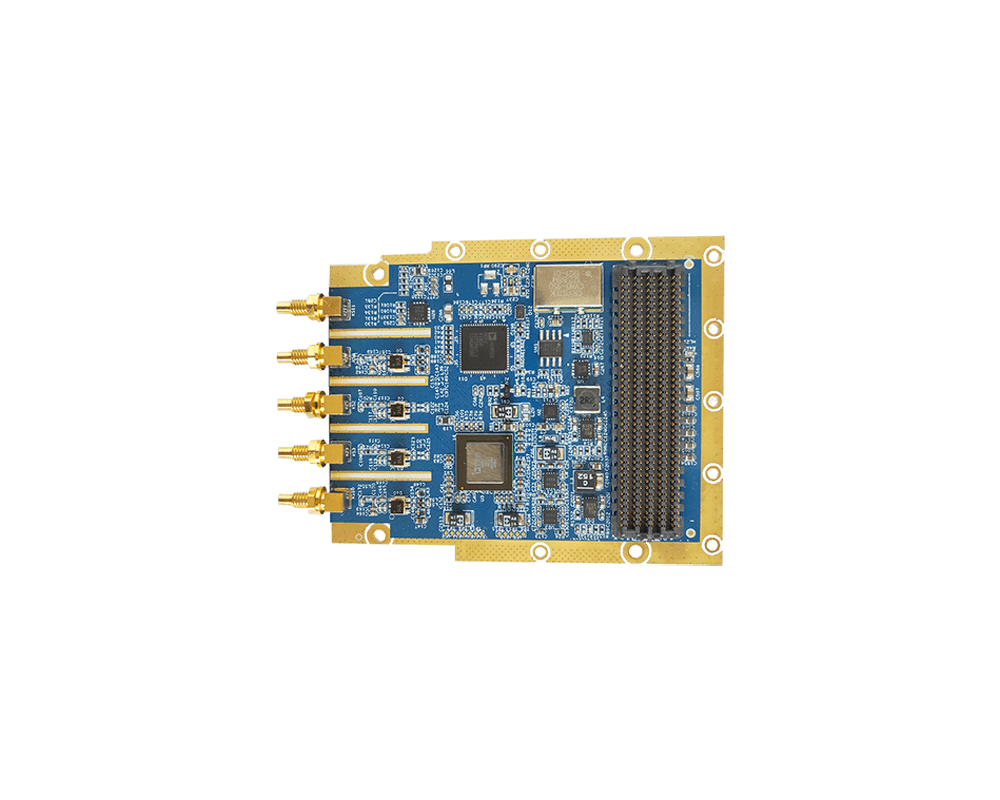

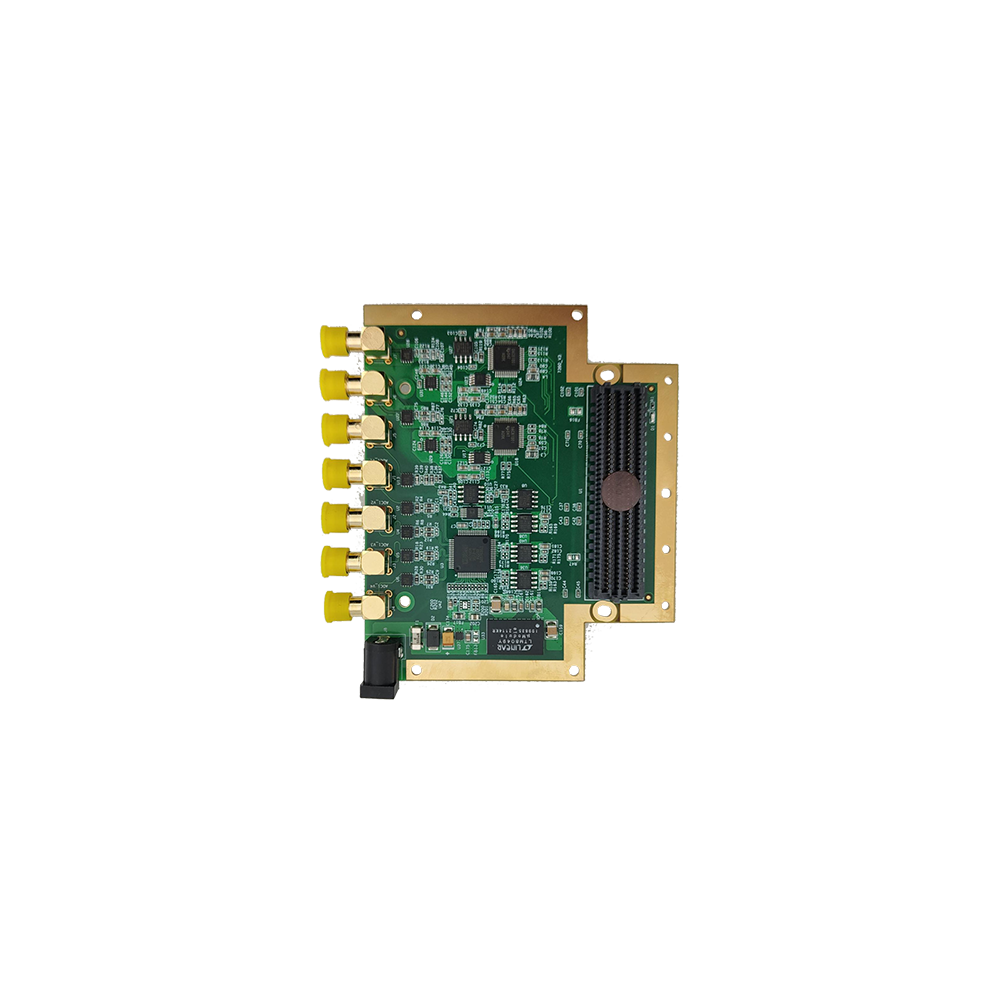

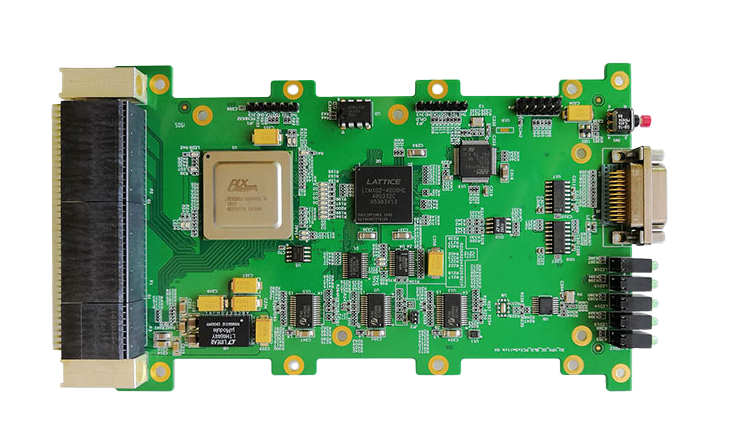

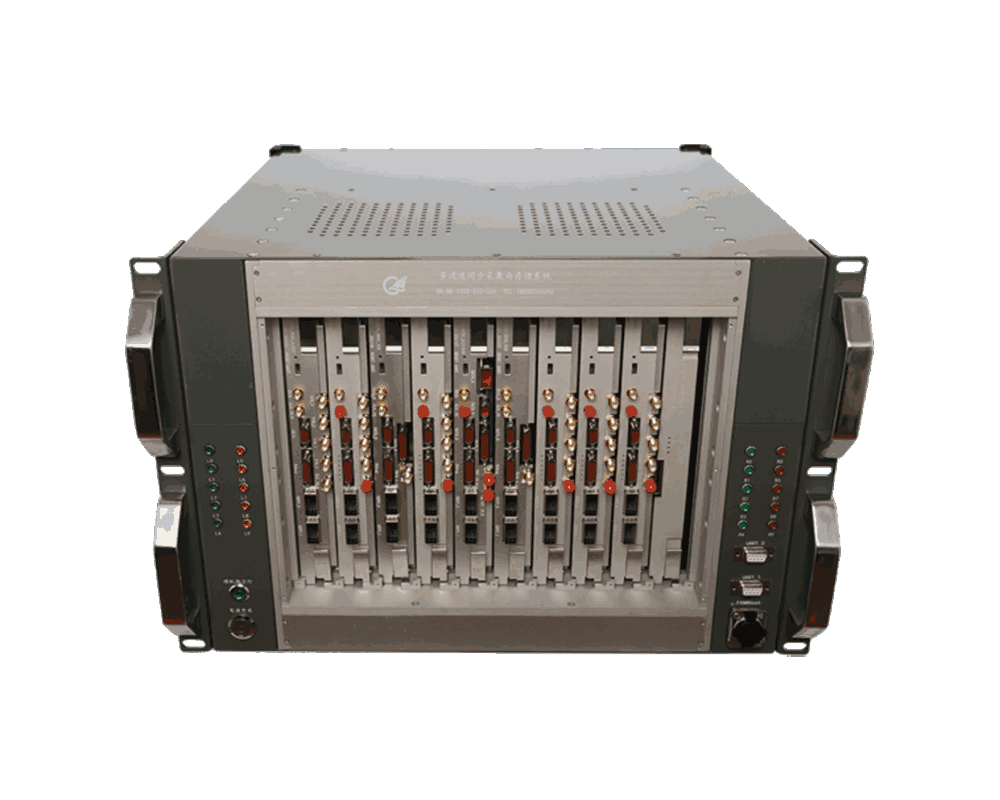

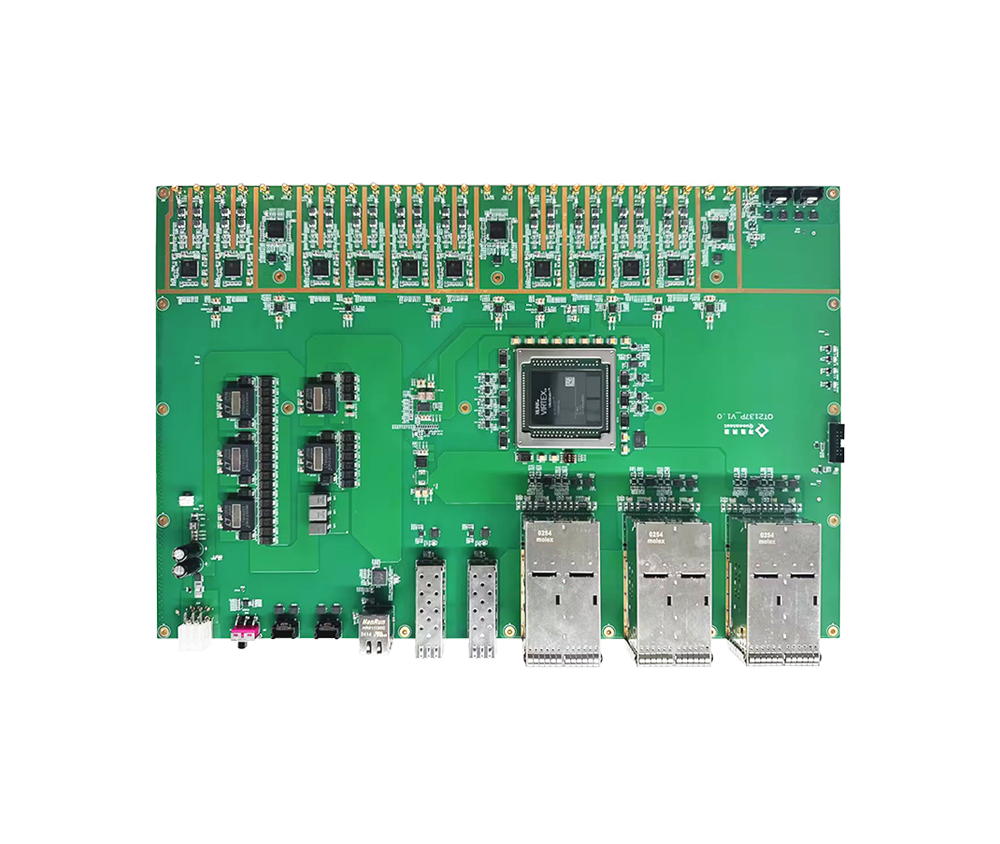

QT2137P-基于VU37P的高性能采集板卡

QT2137P是一款最大可提供20路ADC接收通道的高性能采集板卡。每路A/D通道支持1GS/s的采樣率,分辨率為14bit,模擬輸入帶寬可達500MHz,交流耦合,輸入阻抗50歐姆。

-

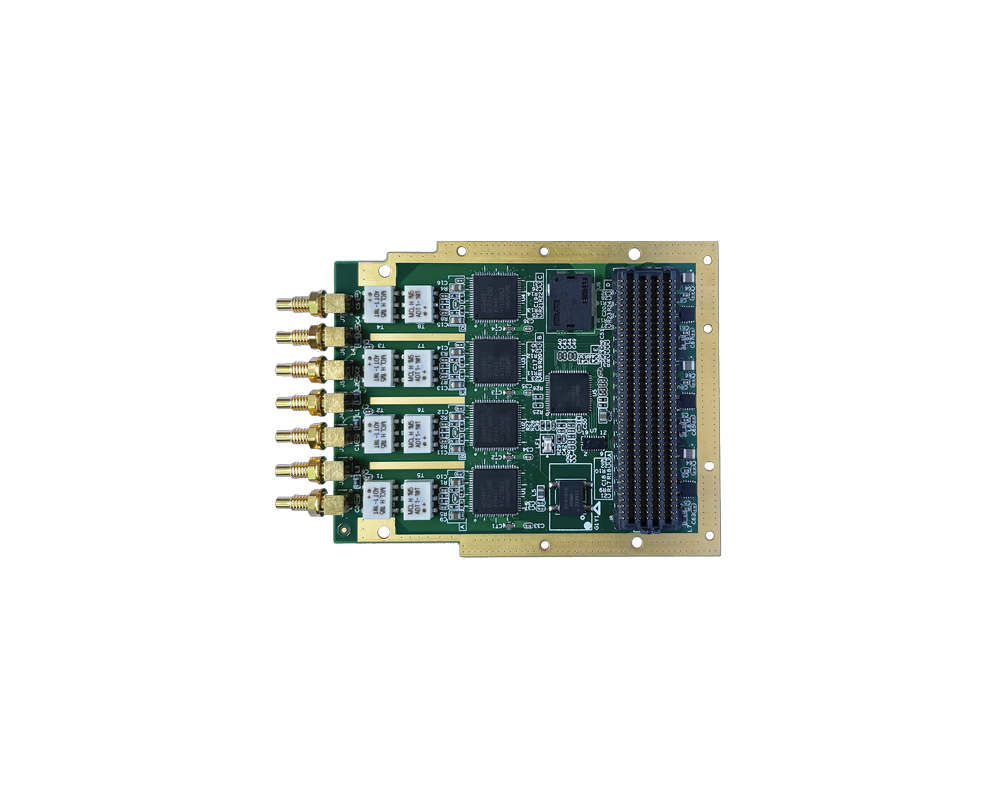

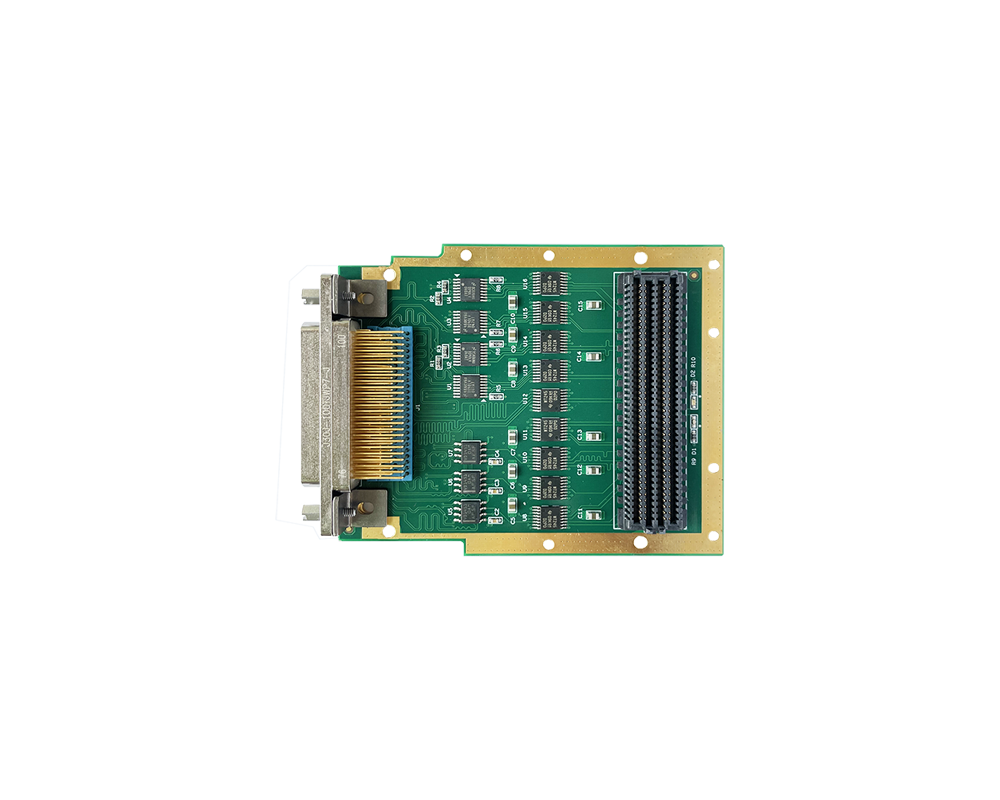

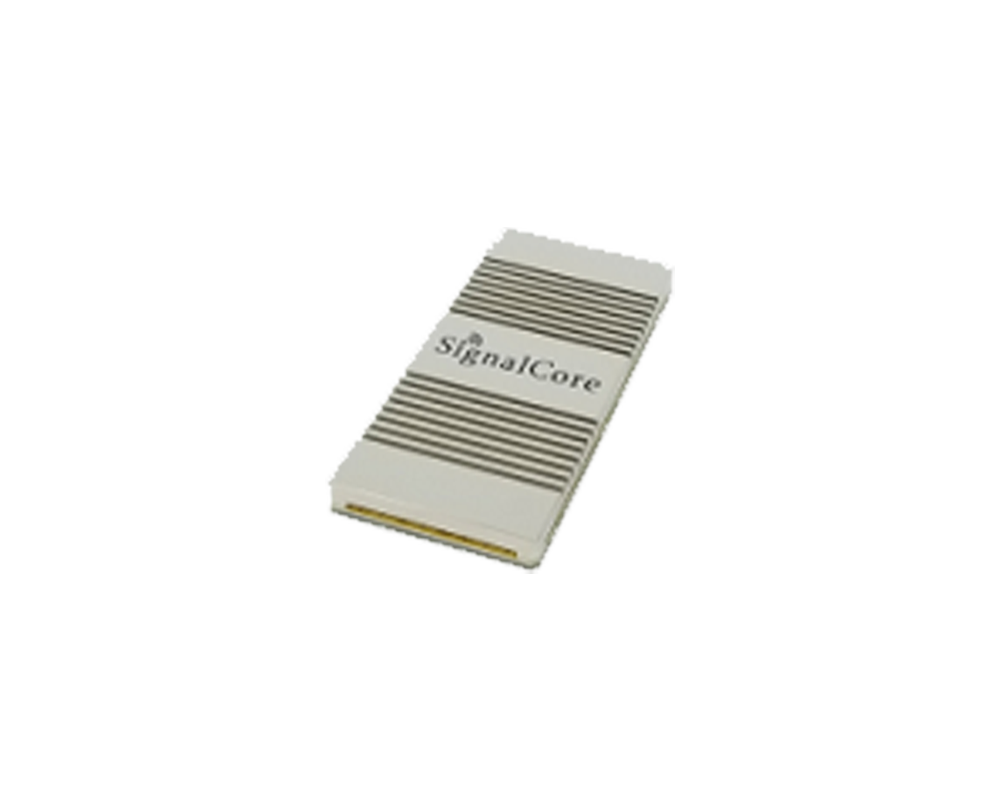

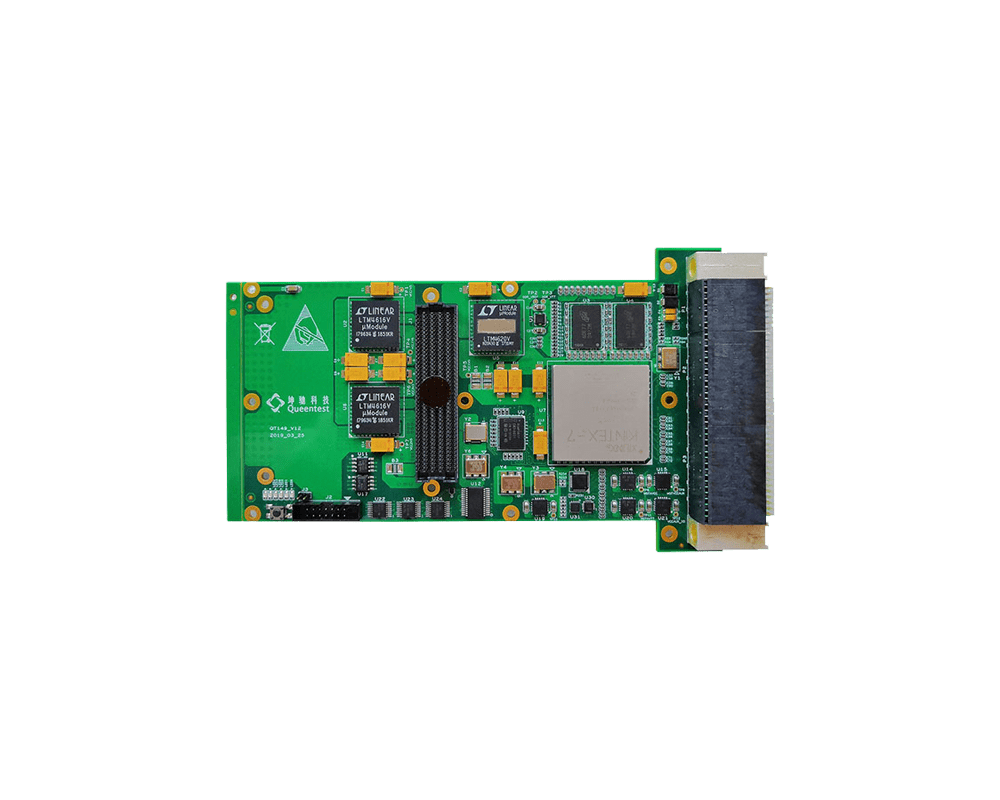

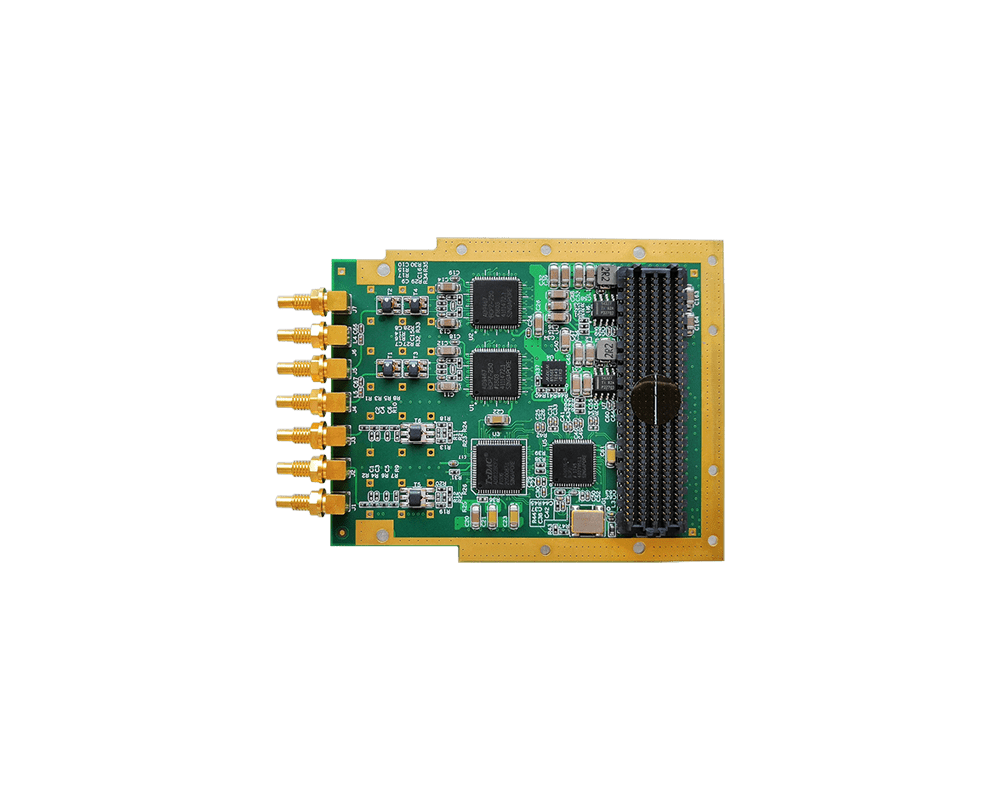

QT7350-FMC AD/DA子卡

2通道,16bit,250MS/s ,ADC和2通道,16bit,500MS/s,DAC

-

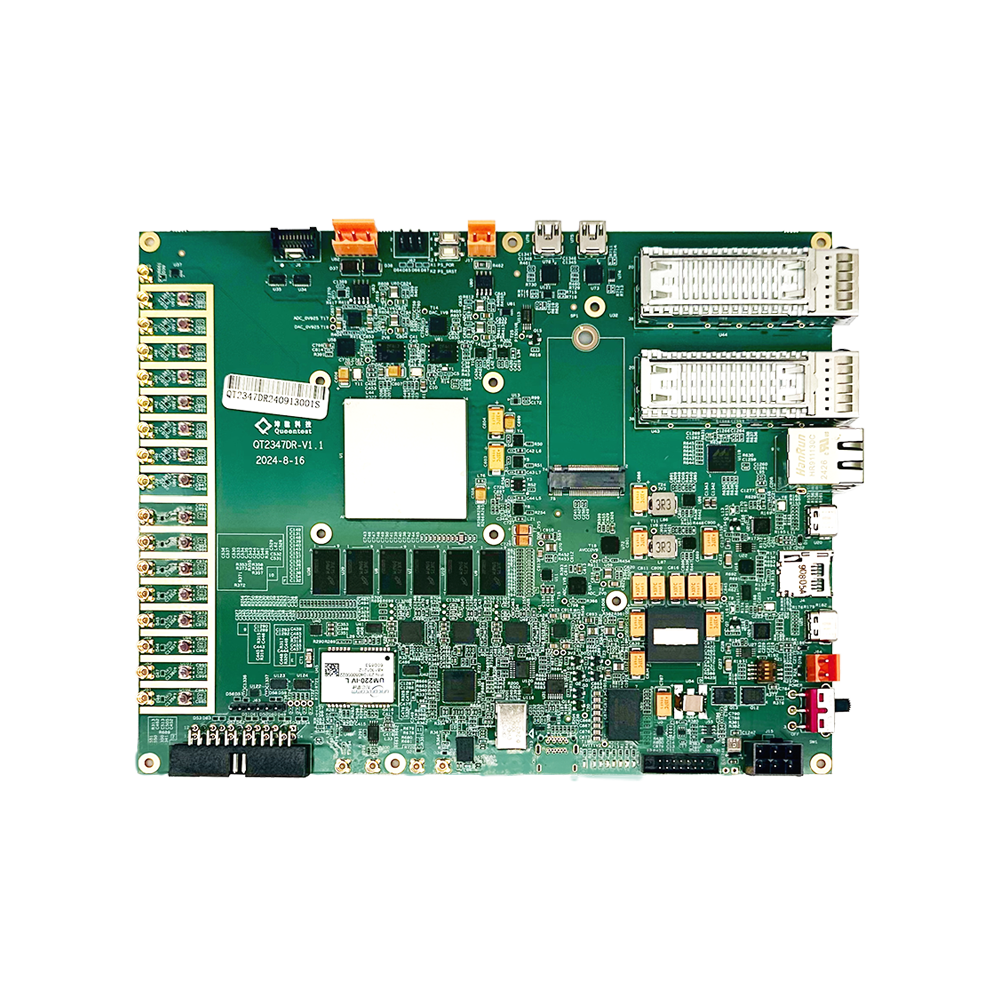

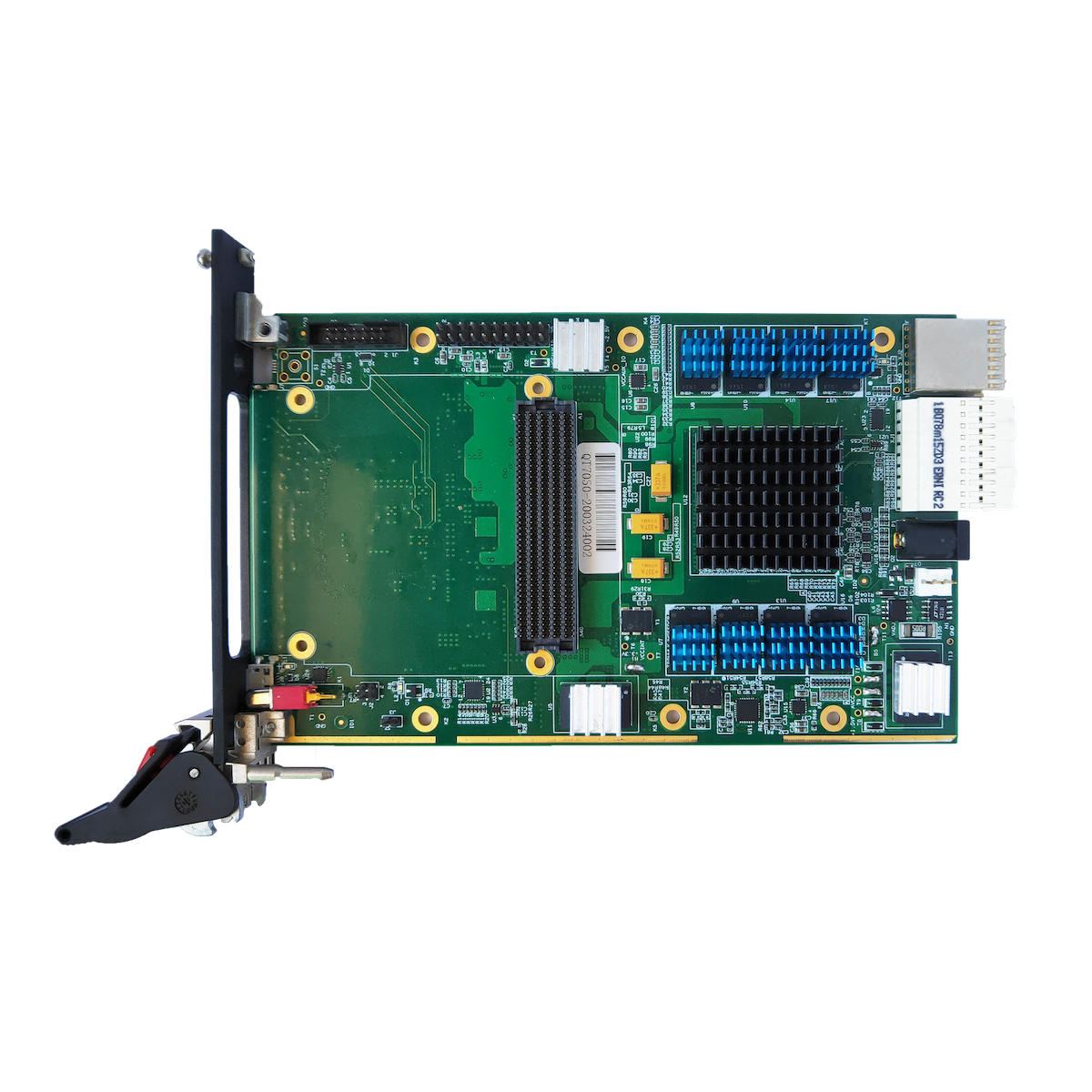

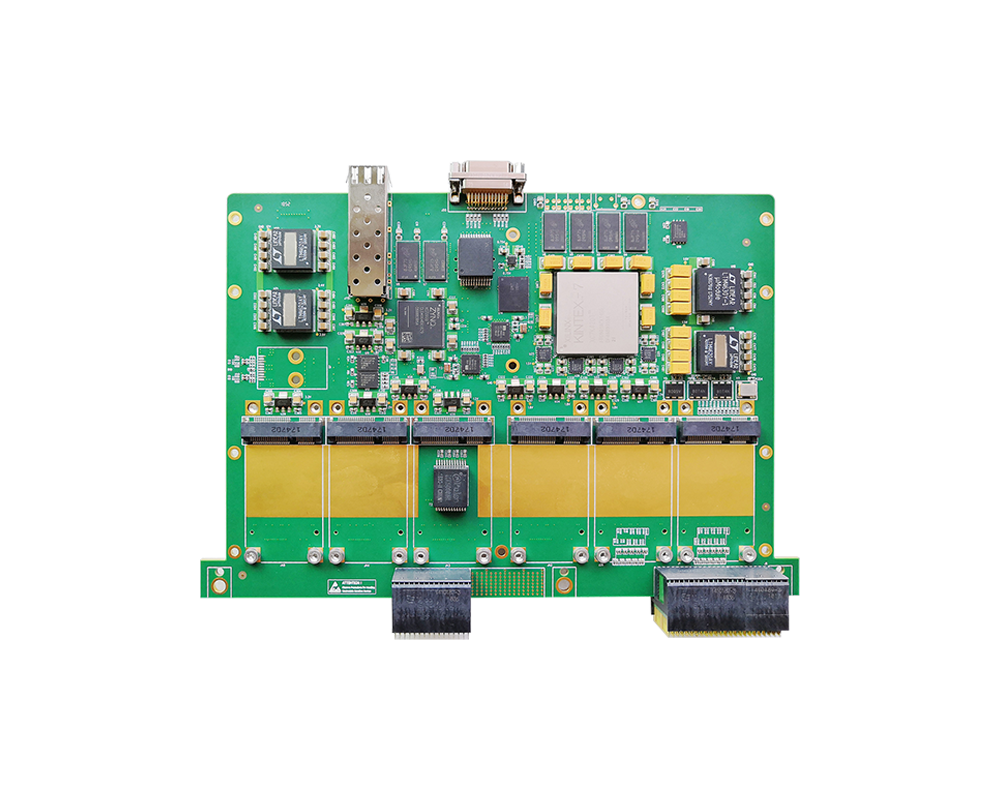

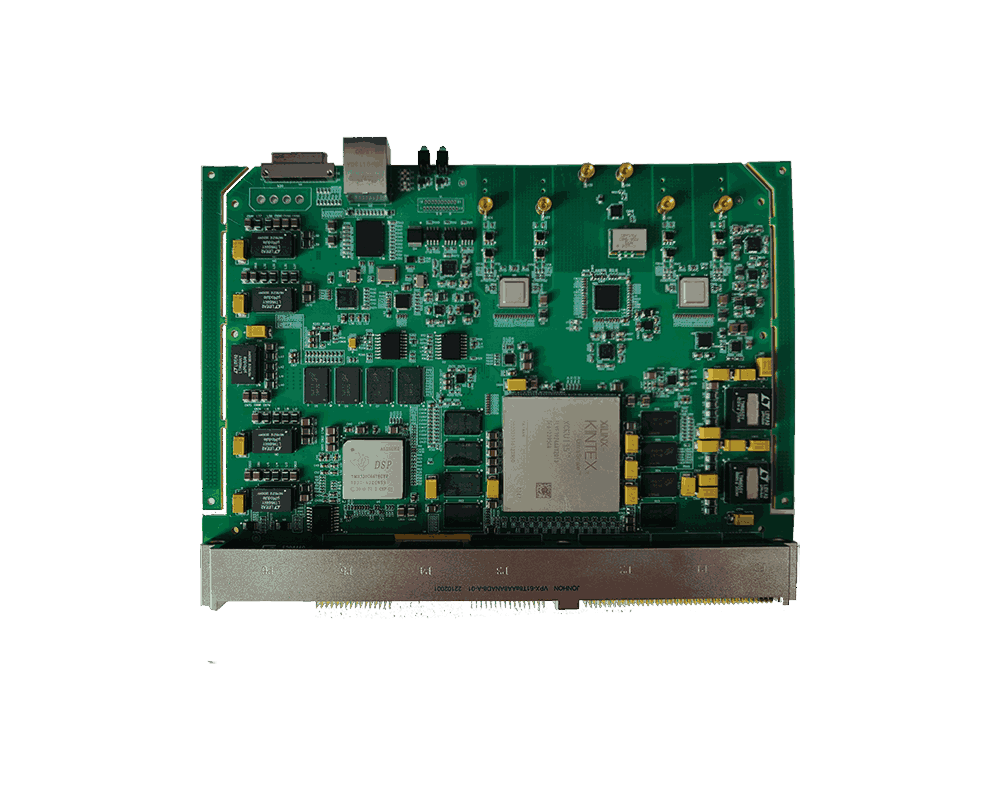

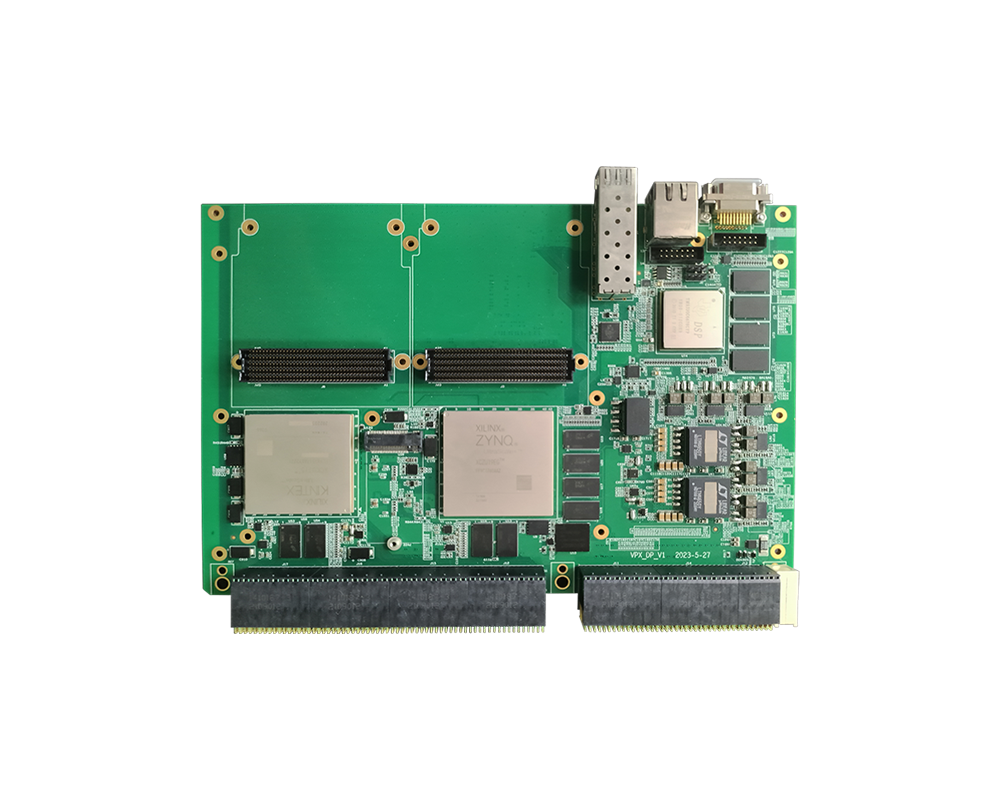

QT7042DSP-6U VPX FPGA載板

FPGA:XCKU115-2FLVA1517I*1 ;XCZU19EG-2FFVC1760I*1 ; DSP :TMS320C6678ACYPA*1 雙FMC 外設接口:SATA,千兆網,萬兆網,J30J等

-

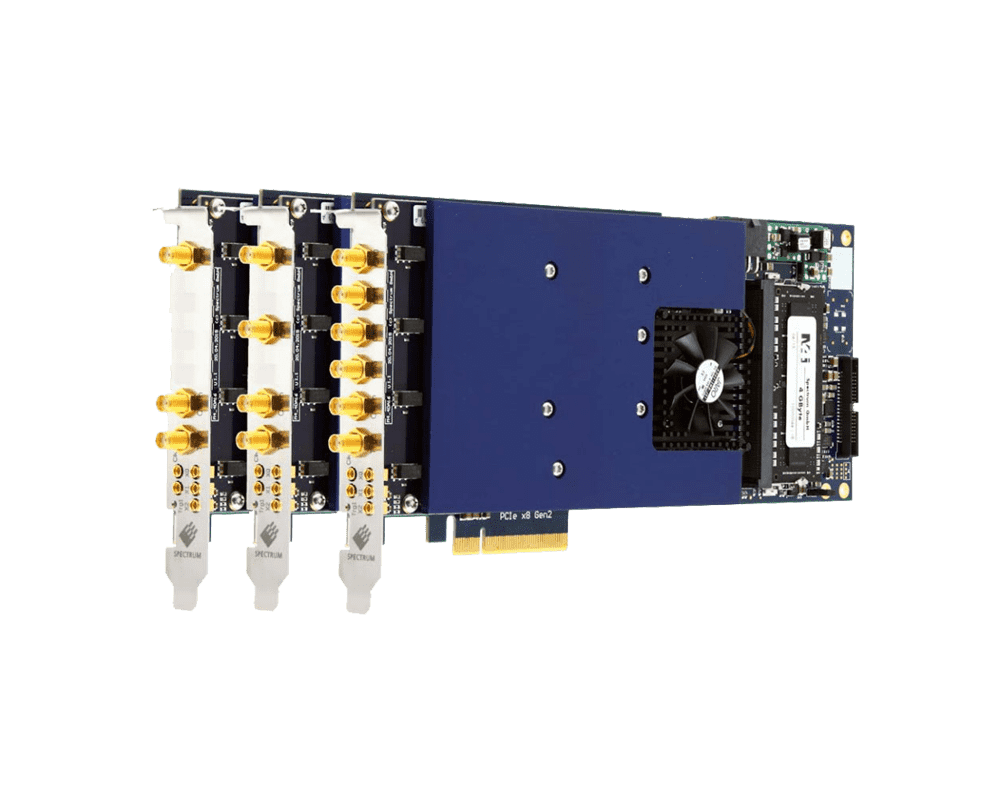

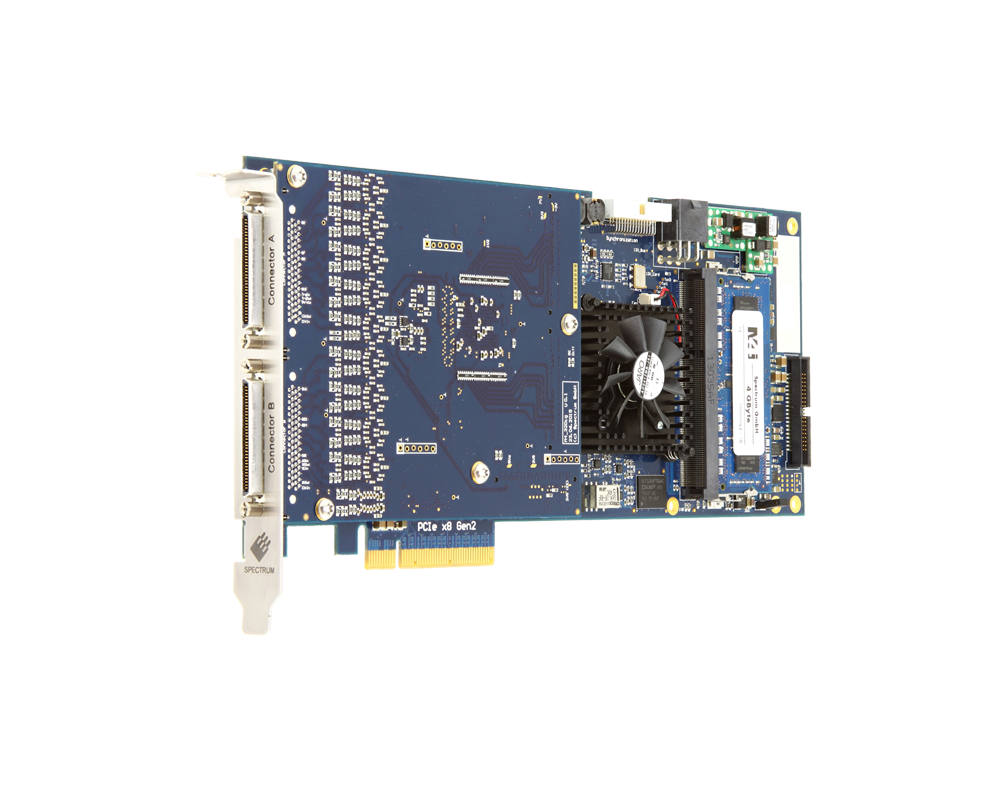

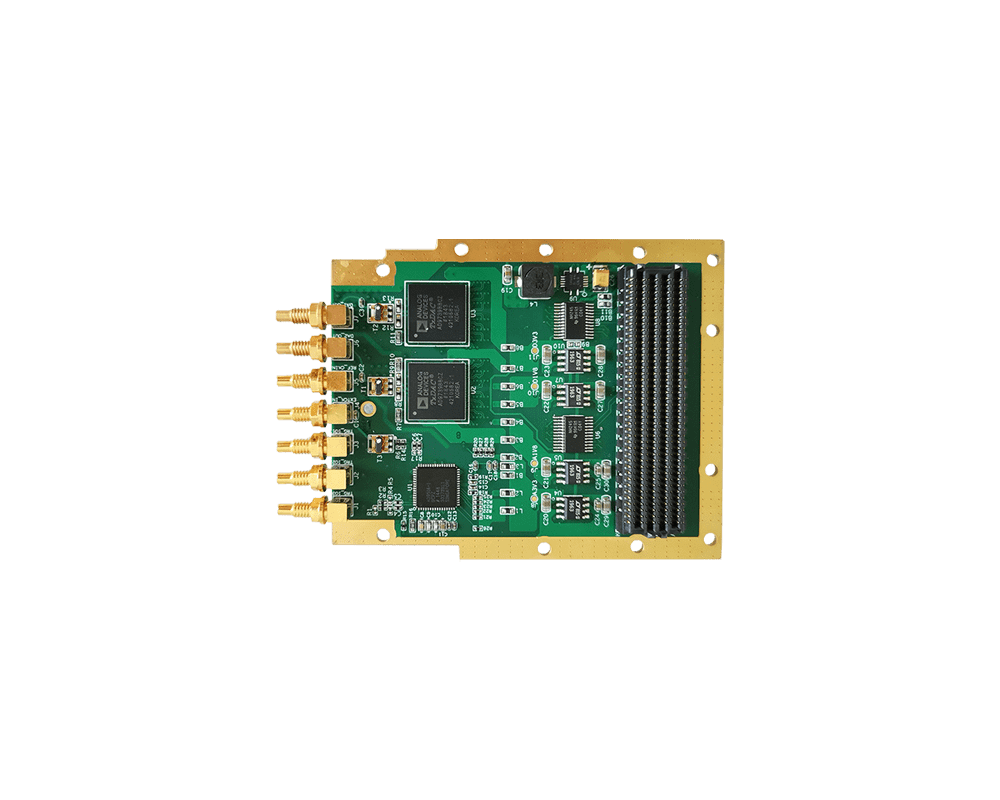

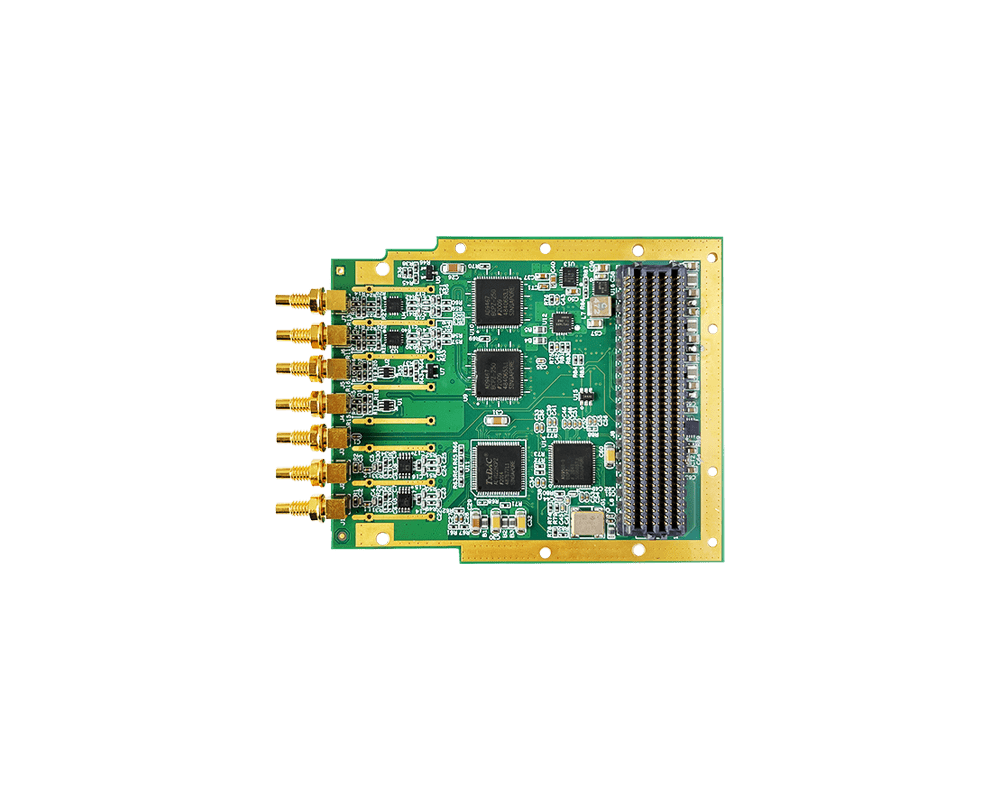

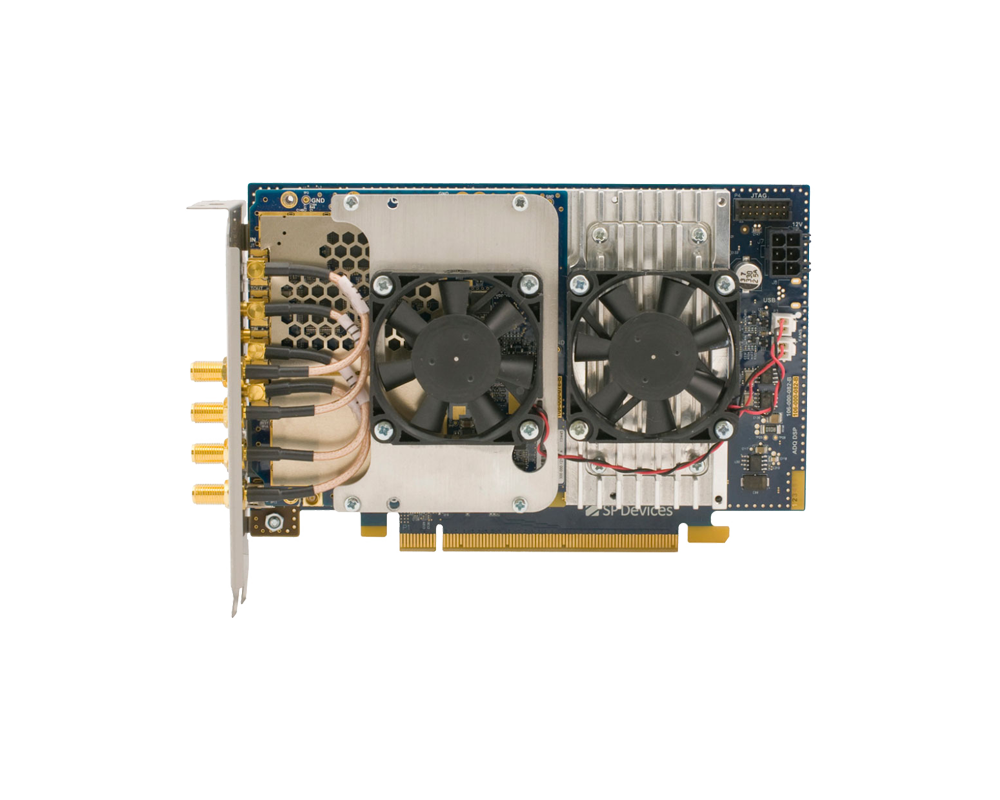

ADQ1600-寬帶中頻采集卡

單通道;14bit;1.6GSPS采樣率;800MHz模擬輸入帶寬及500MSamples板載內存;適用于例如IF/RF采樣及高速數據記錄等不同的應用場合