高速脈沖信號采集與特征判別系統(tǒng)|窄脈沖信號|脈沖信號采樣

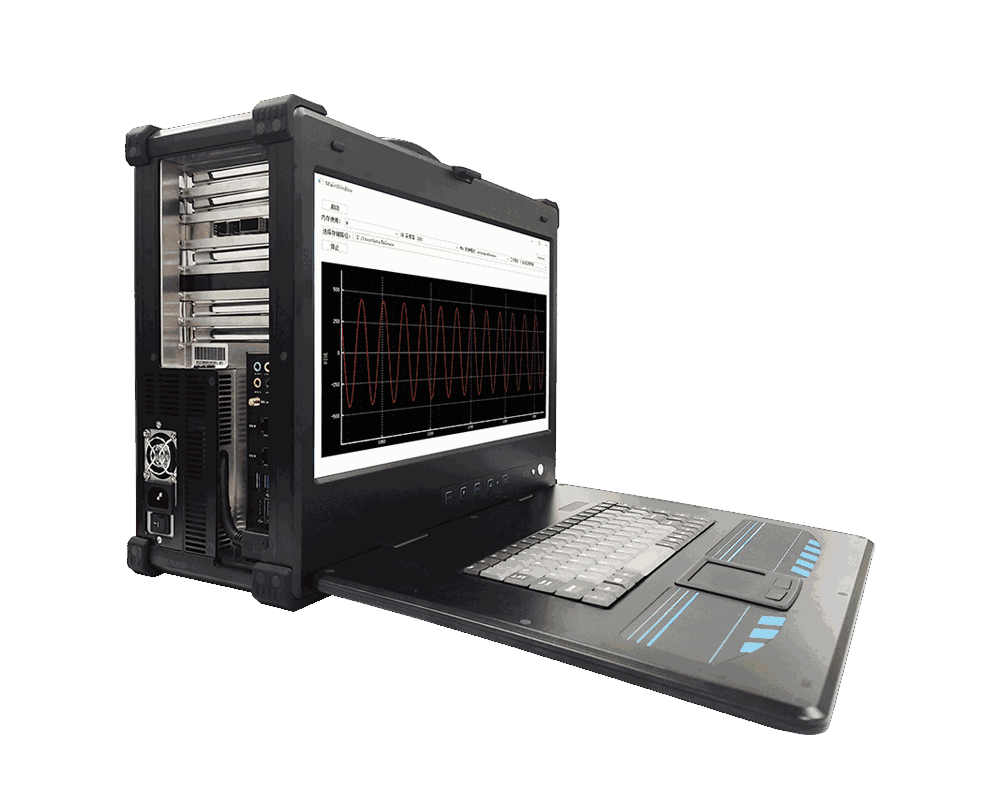

一、概述:

項目背景:

該項目主要用于光脈沖在不同介質(zhì)中的傳輸特性不同,來實現(xiàn)對目標的跟蹤。

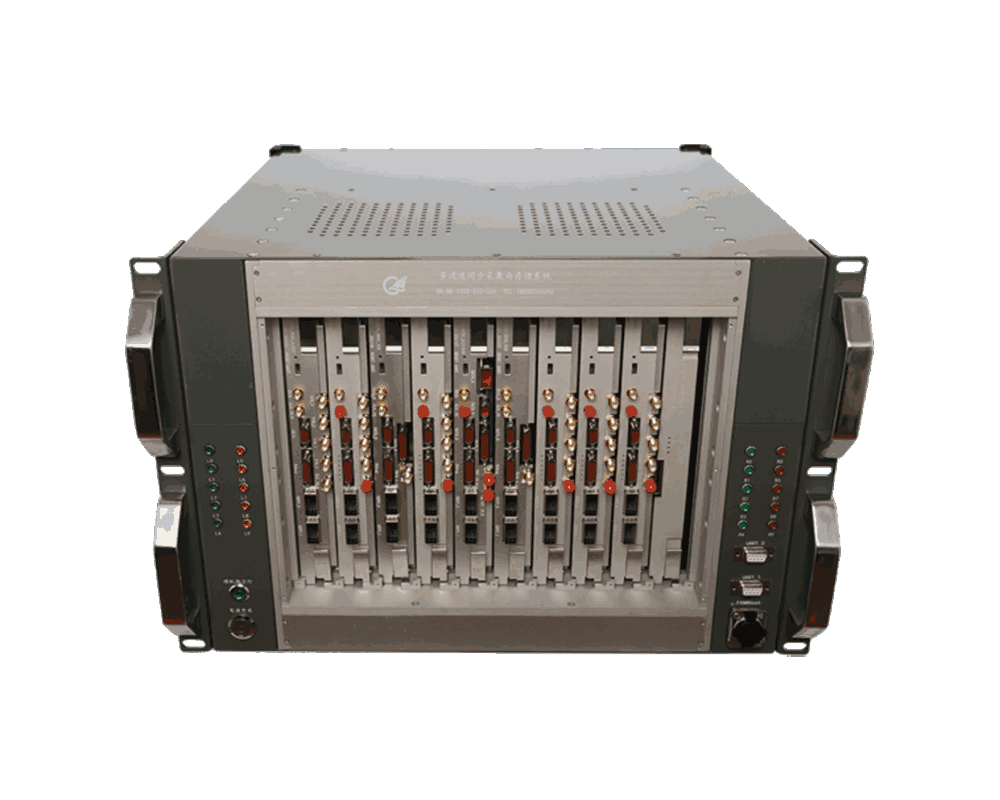

本系統(tǒng)主要應(yīng)用于水下目標的特征探測。

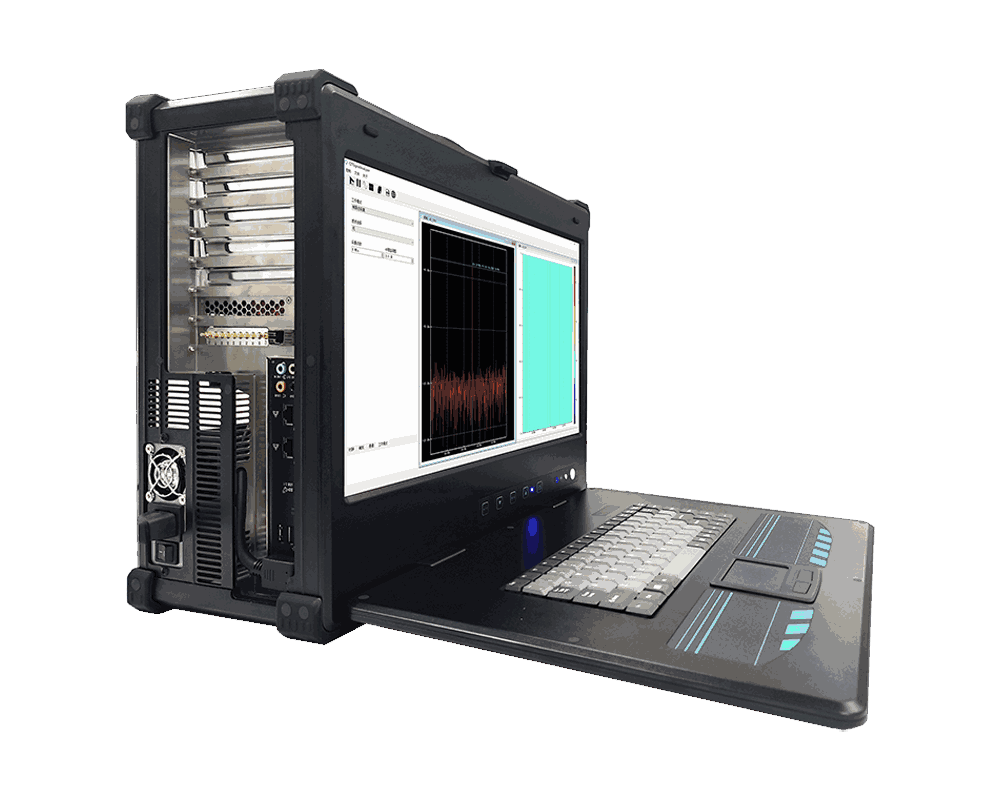

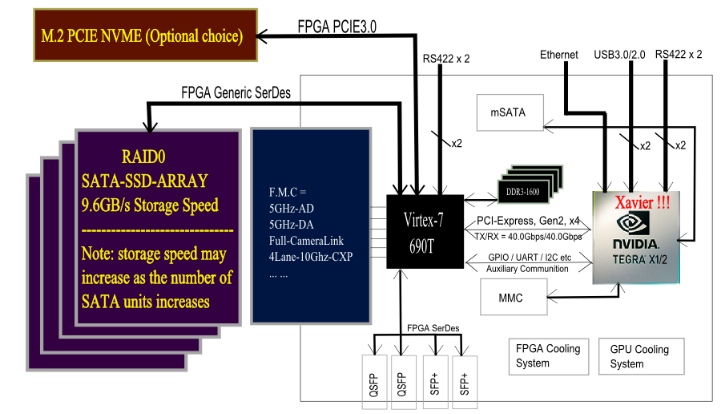

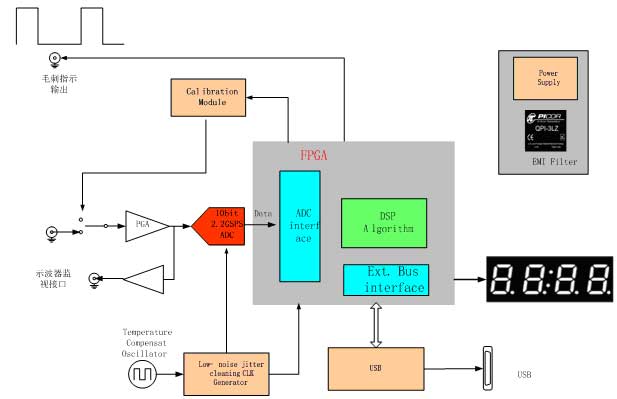

系統(tǒng)框圖如下:

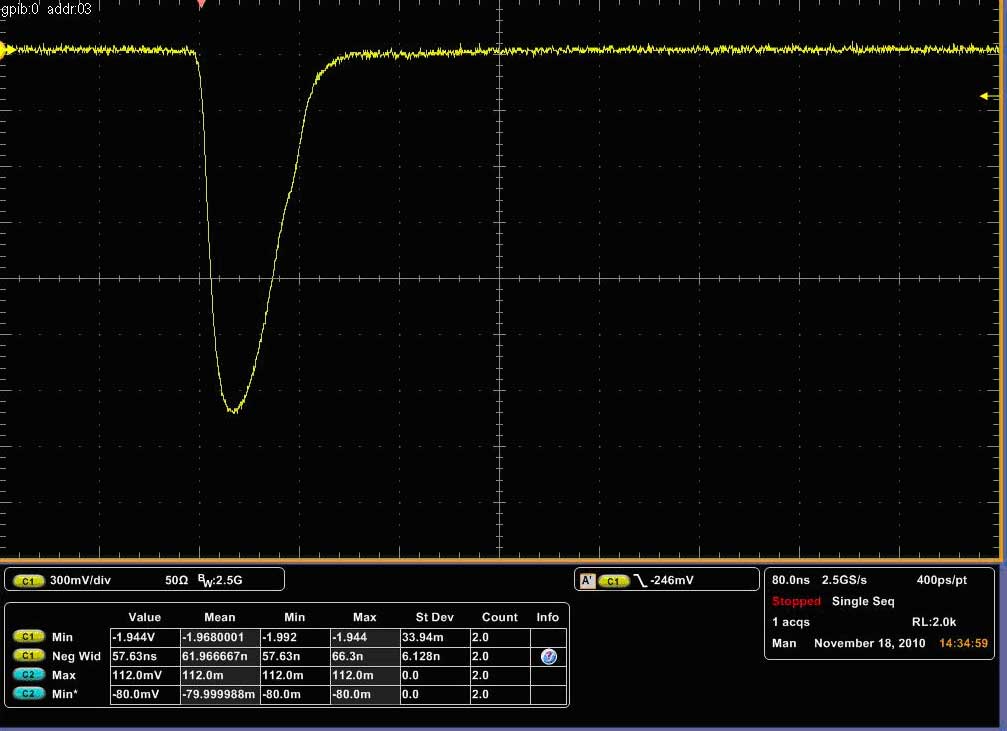

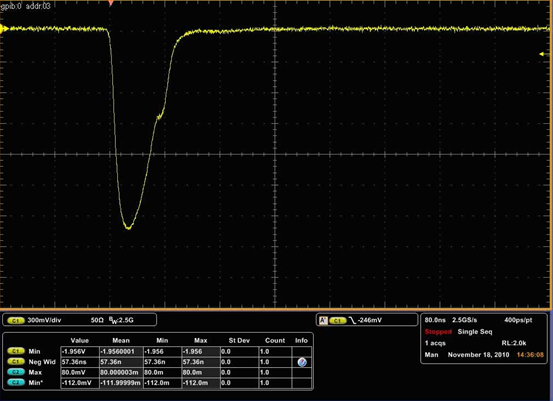

當光電倍增管接收的光為均勻的介質(zhì)是產(chǎn)生的經(jīng)典本底信號如下:

本底信號采用2.5Gsps采樣,下降時間約40ns。

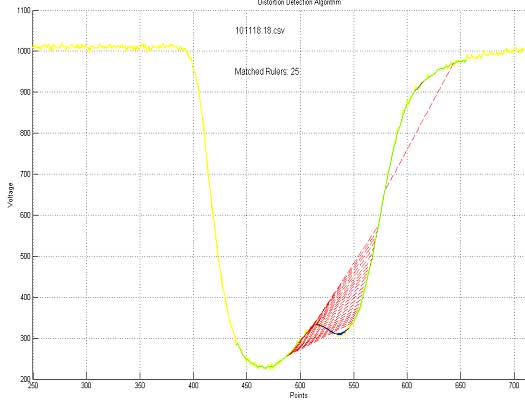

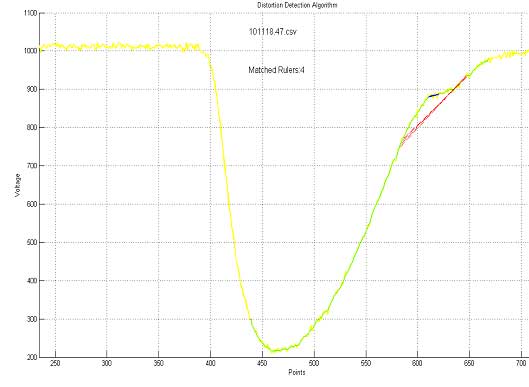

當光電倍增管接收的光為遇到介質(zhì)中的“氣泡”時,將在上圖的本底信號的上升沿產(chǎn)生畸變,典型信號如下:

由于氣泡的位置和大小不確定,所以會產(chǎn)生不同的畸變大小、形狀且畸變的位置也是不固定的。

我們的任務(wù)就是需要采集到光電倍增管輸出的高速脈沖,通過FPGA實現(xiàn)數(shù)字信號實時處理,判別和區(qū)分開當前的信號是本底信號還是有畸變的信號,將該信號的特征上傳到主機。

我們面臨的挑戰(zhàn):

1、光電倍增管輸出的脈沖信號非常的窄,且上升時間特別陡峭;這就需要我們采用高速ADC進行采集。

2、脈沖信號為負脈沖,且幅度較小;這就需要特殊設(shè)計ADC的前端放大器,采用高速高帶寬直流放大器并且增加高穩(wěn)定度偏置電路。

3、水下環(huán)境復(fù)雜,有時本底信號和有氣泡的信號區(qū)別不是很大,這就需要設(shè)計更復(fù)雜的算法進行更精確的分析和判別;算法復(fù)雜程度較大。

4、本底和畸變差別較小本底和畸變差別中等本底和畸變差別較大。

5、由于采用高速采集,采集時鐘為2GHz,遠高于FPGA所能接收的速度,所以需要采用并行計算的方式來實時處理采集到的信號。

解決方案:

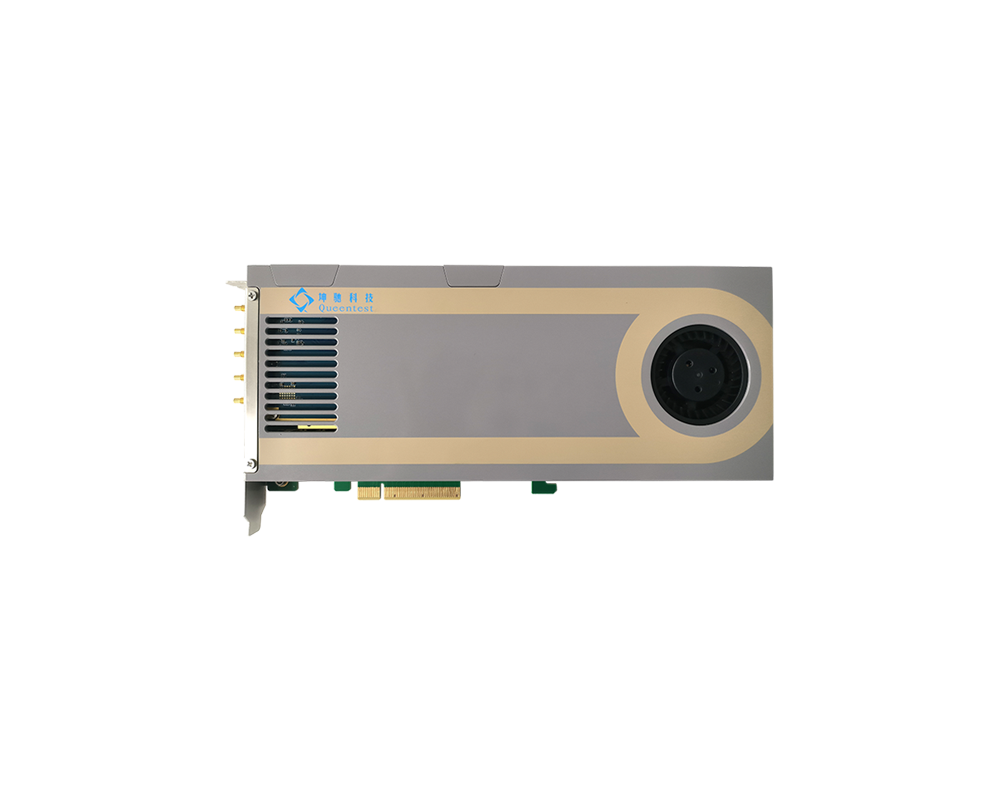

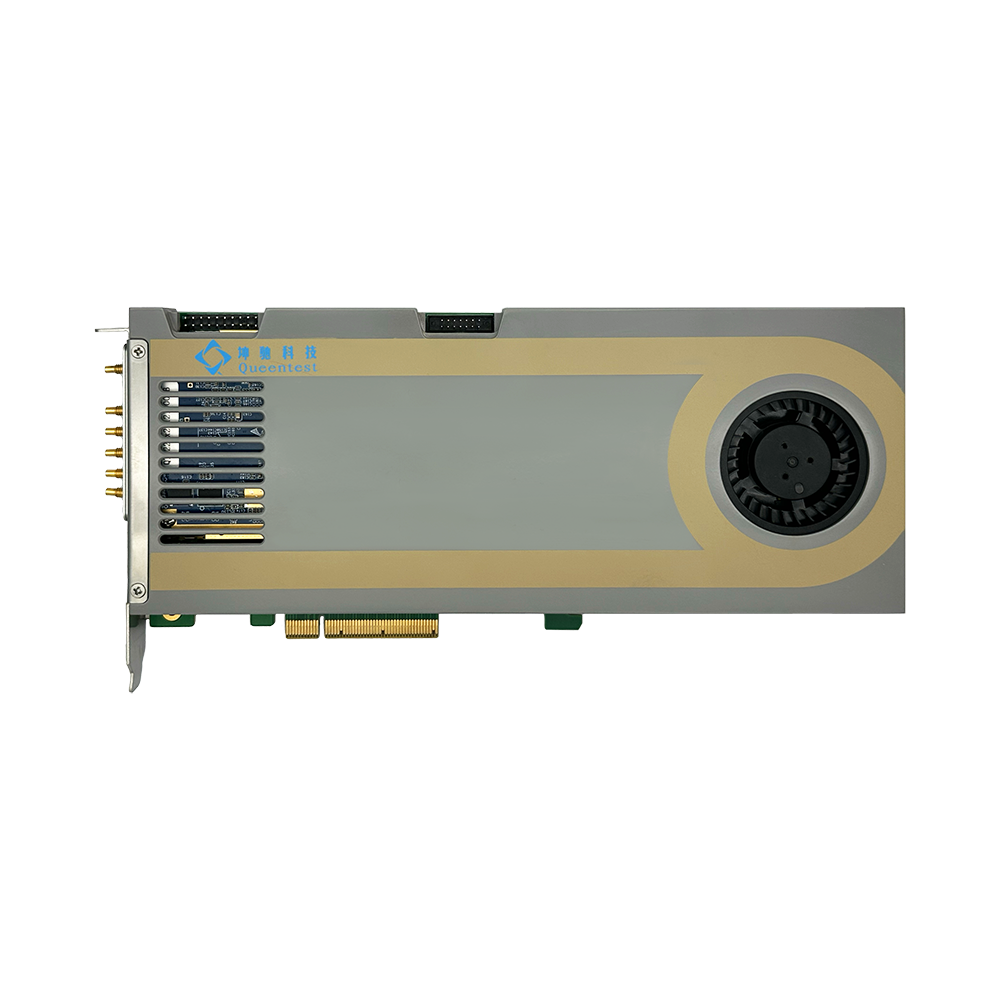

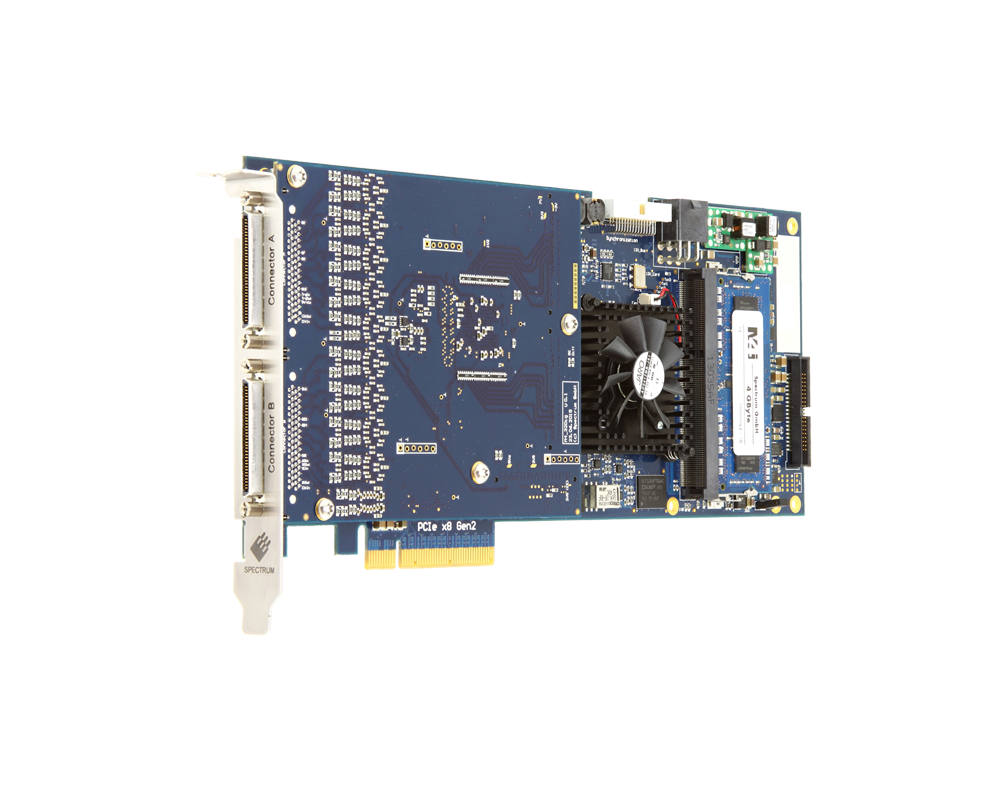

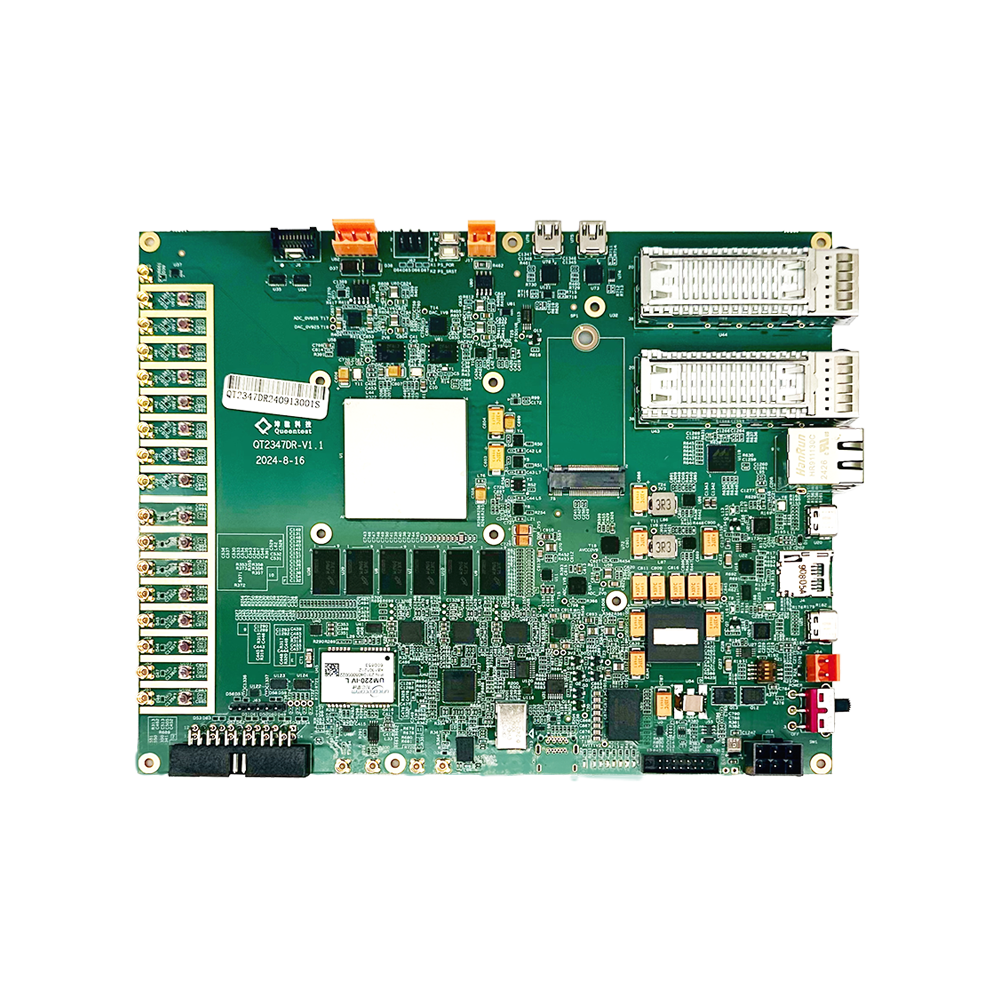

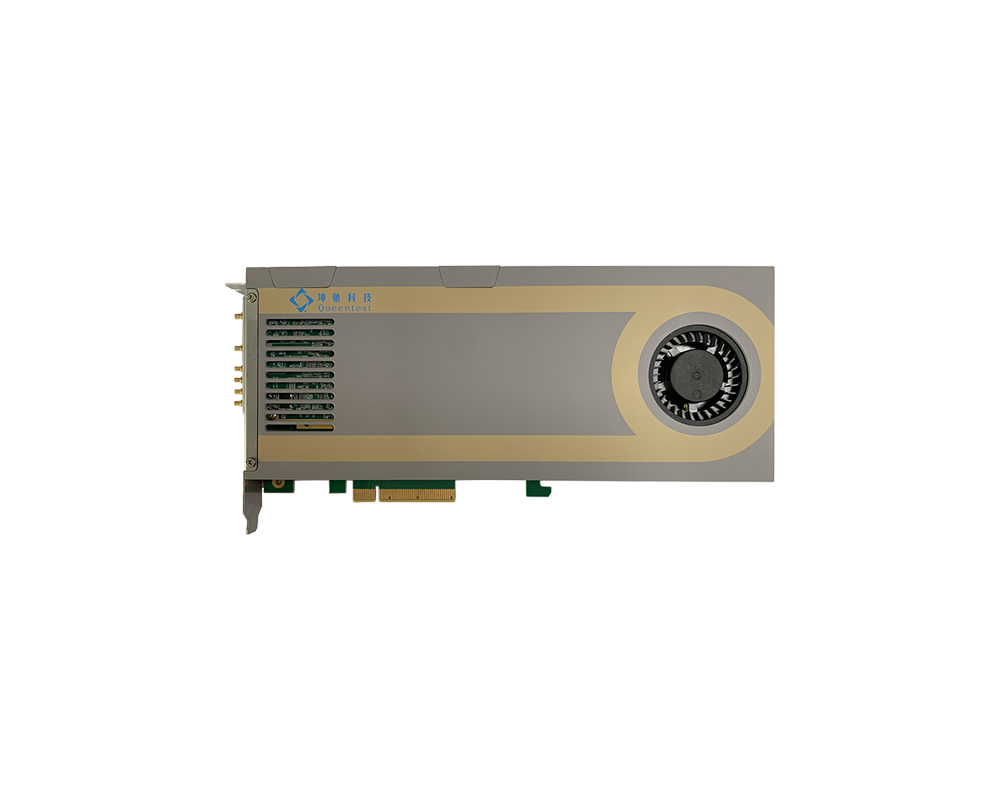

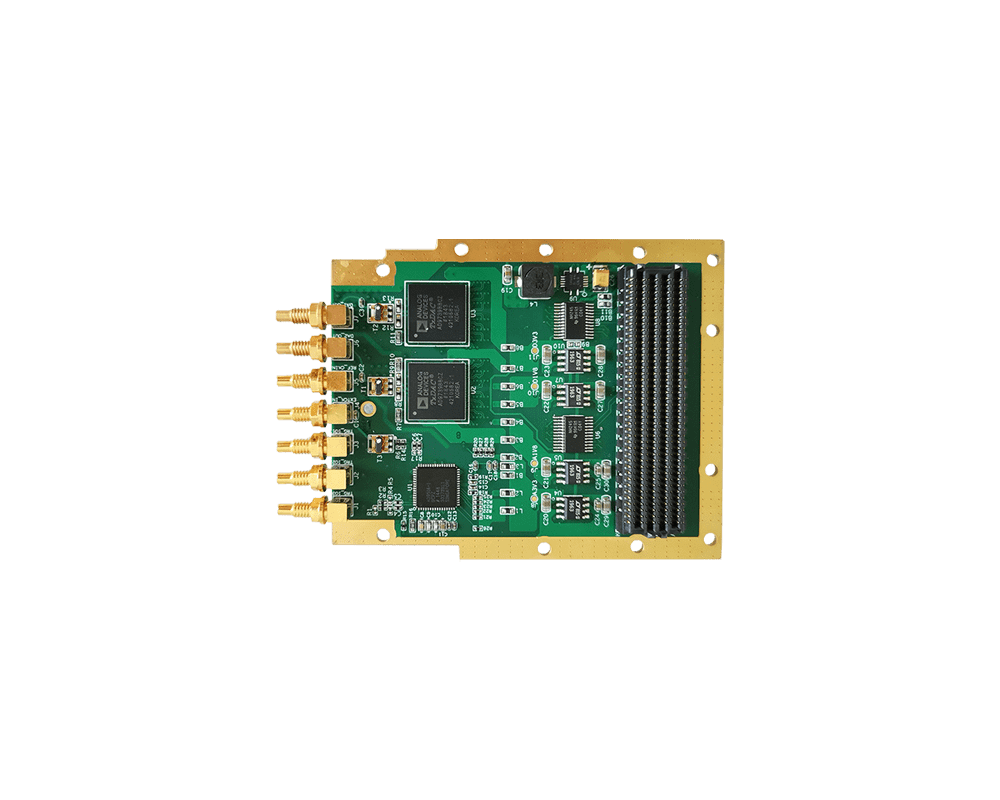

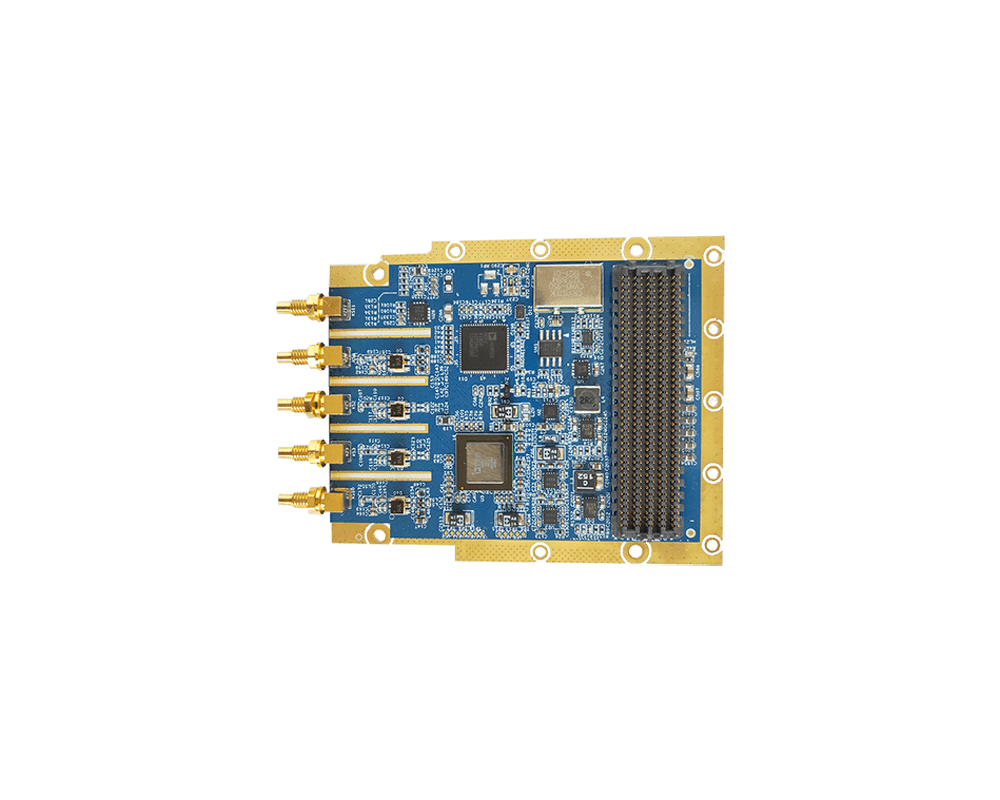

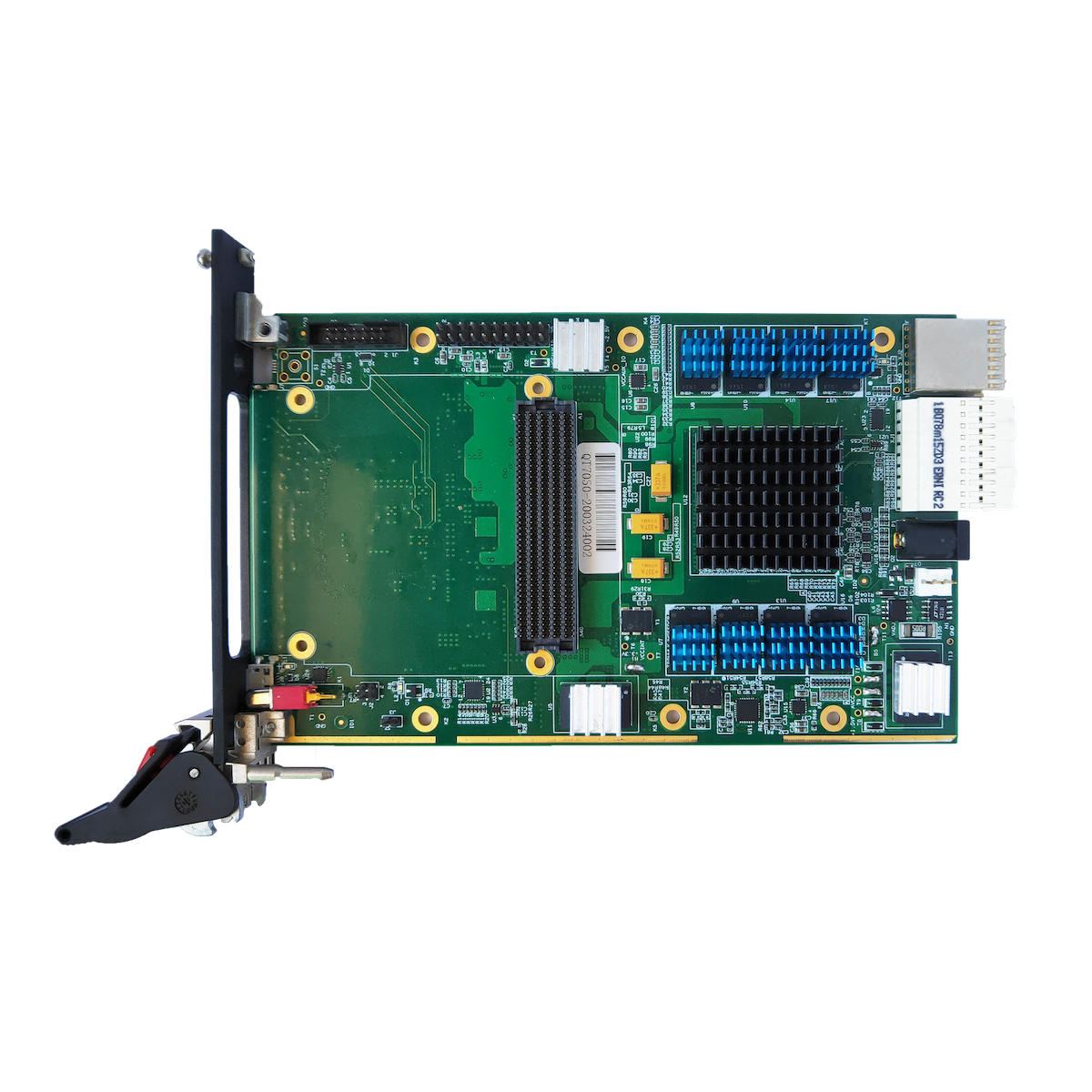

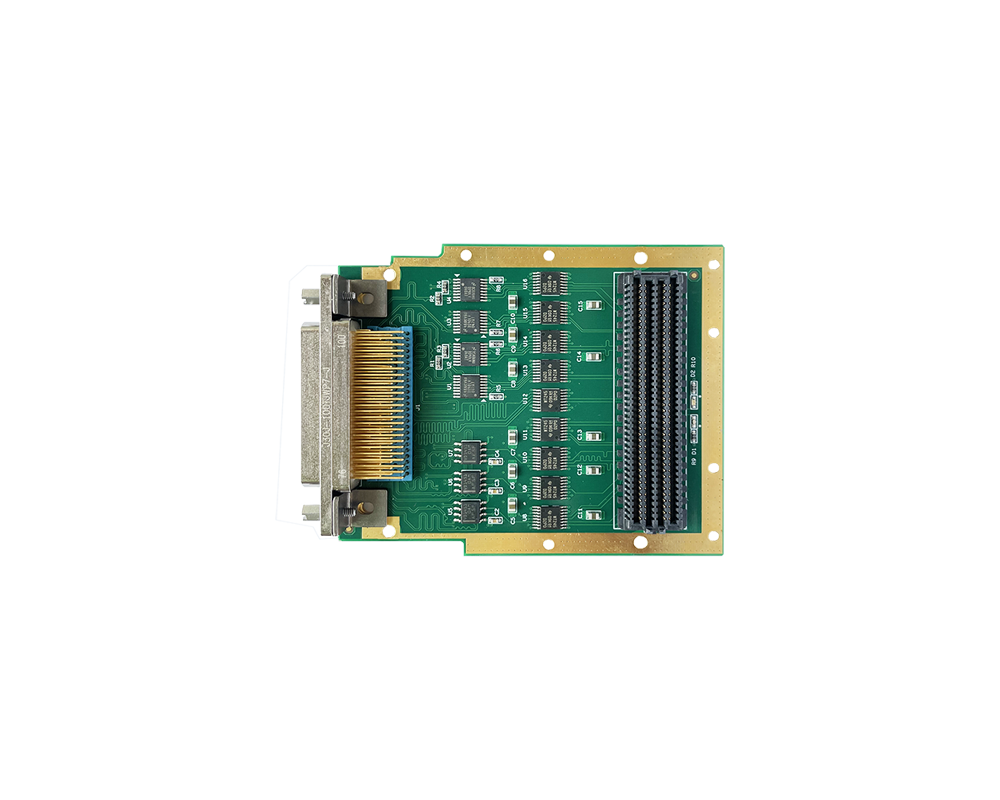

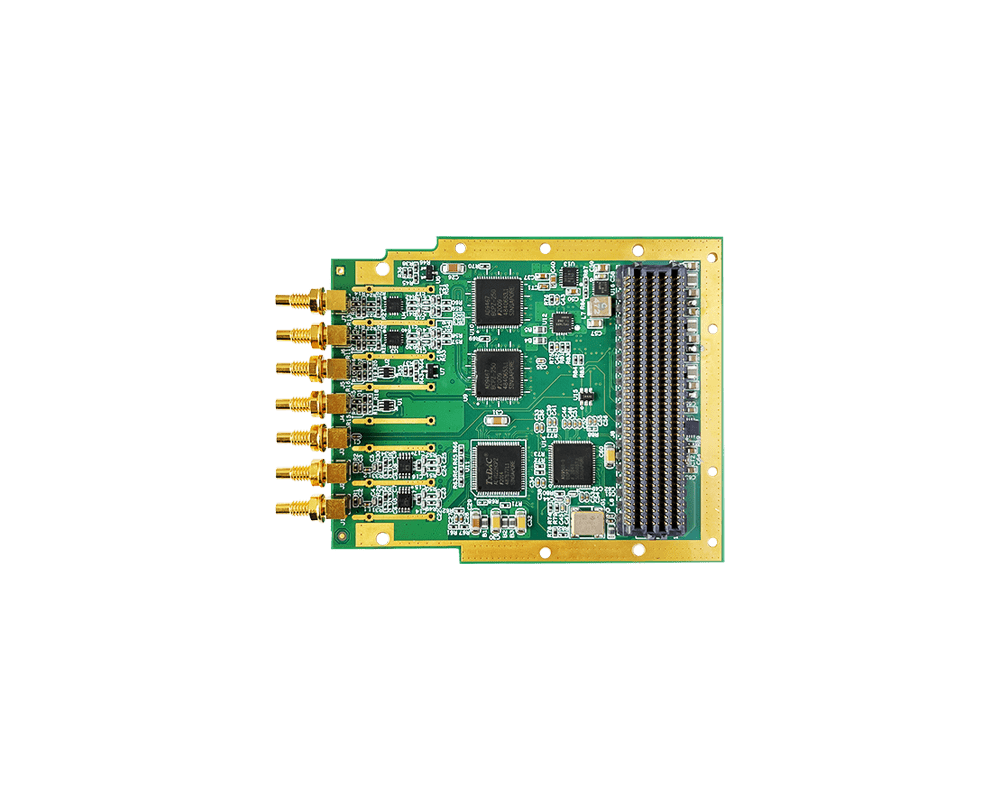

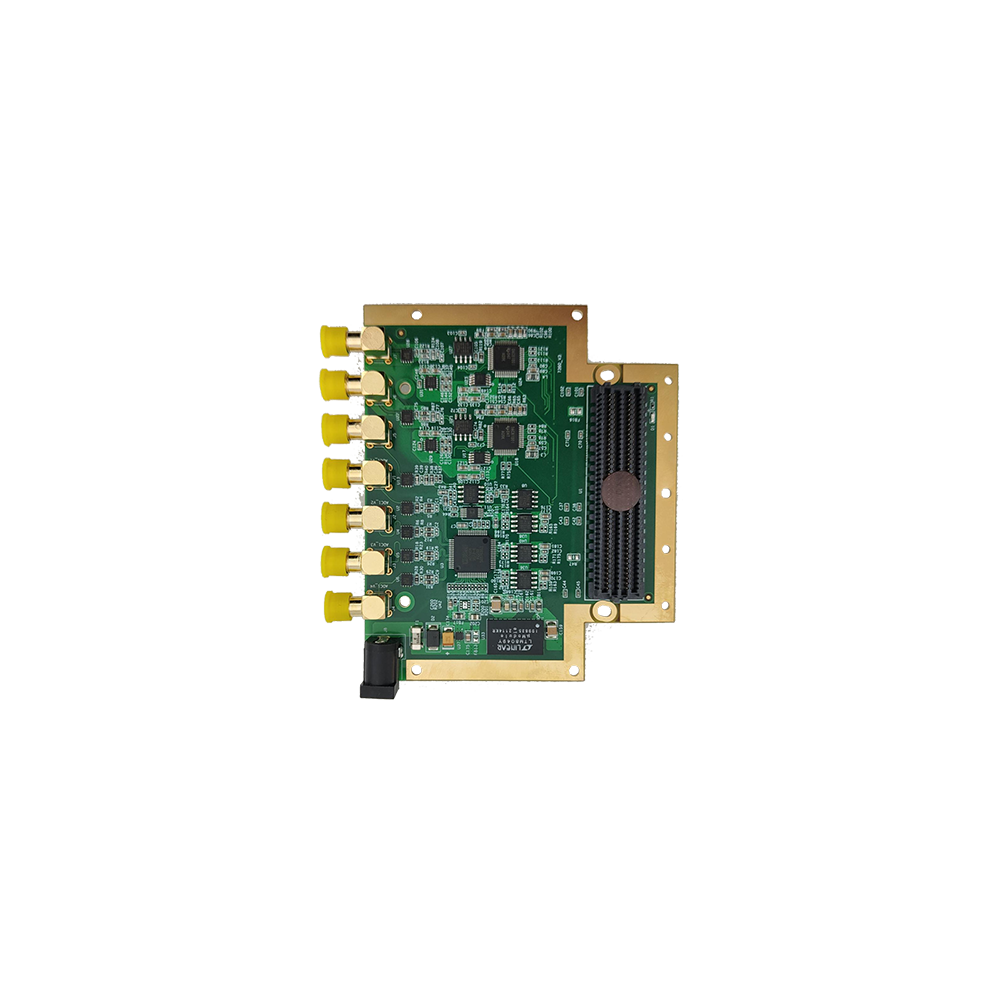

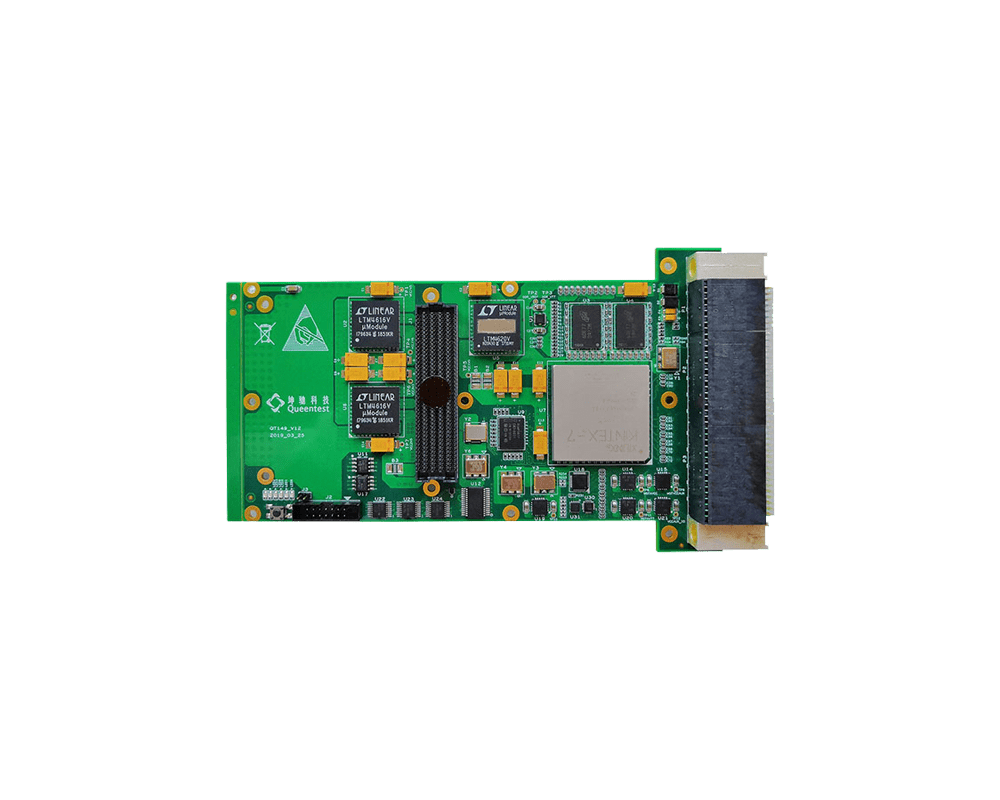

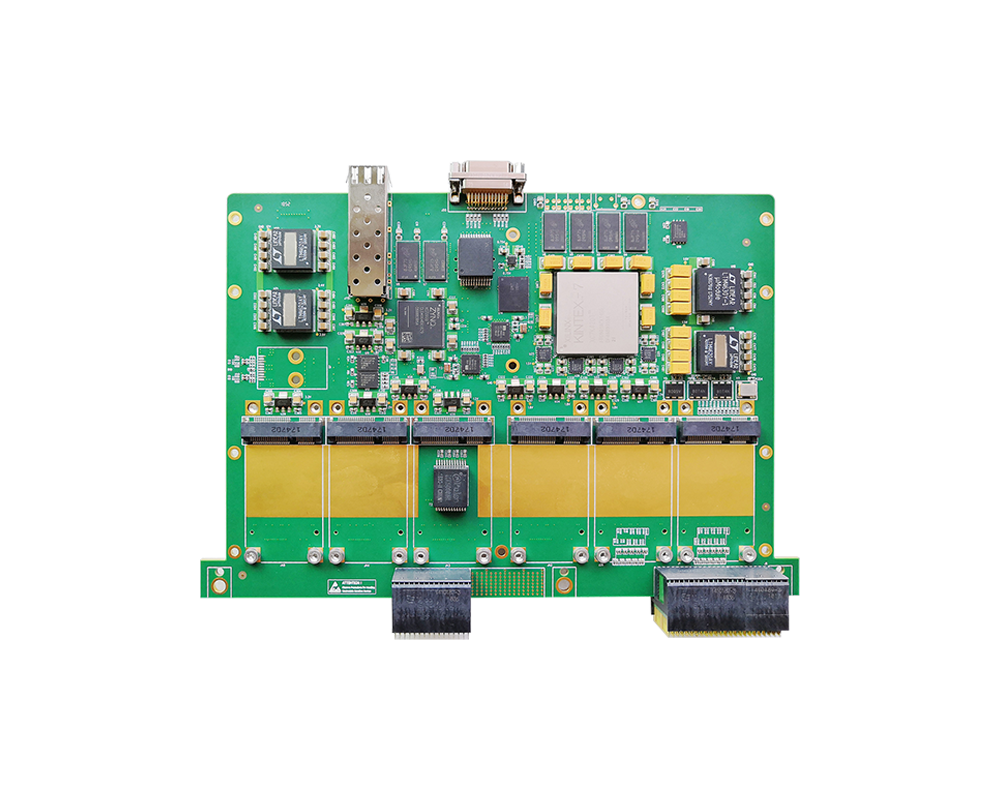

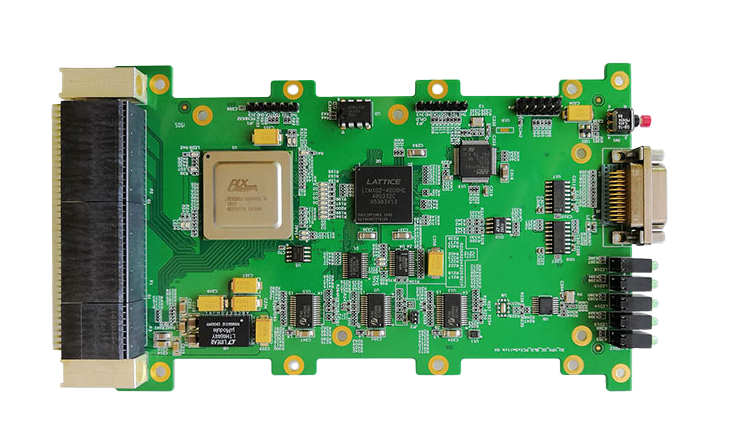

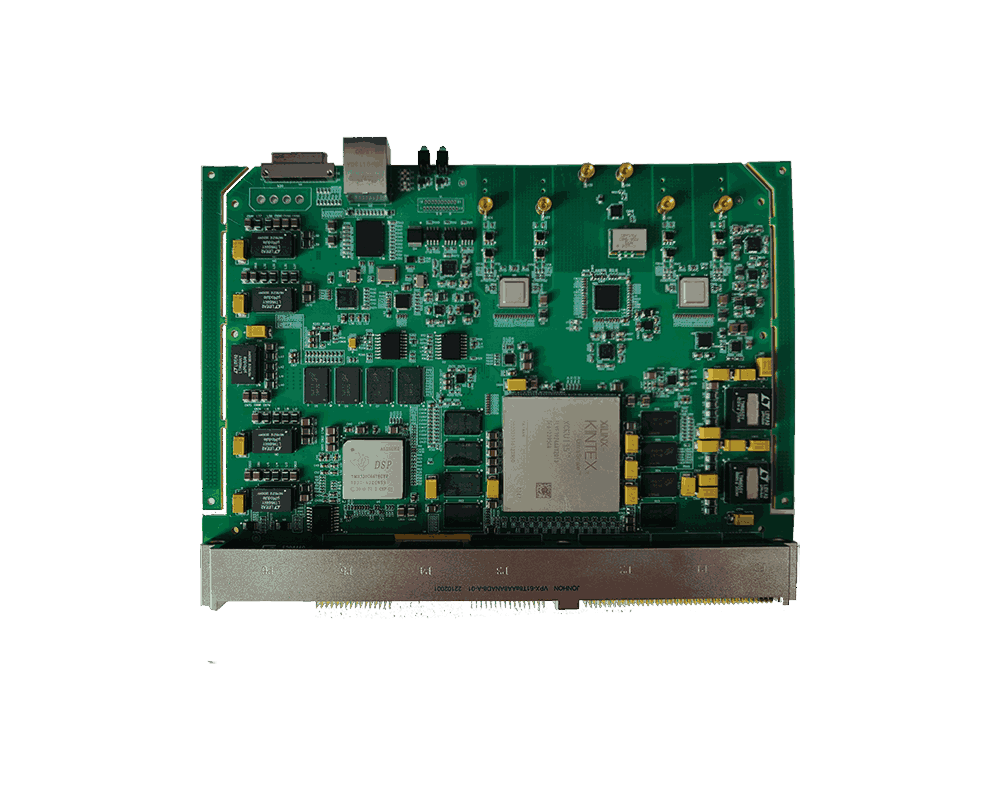

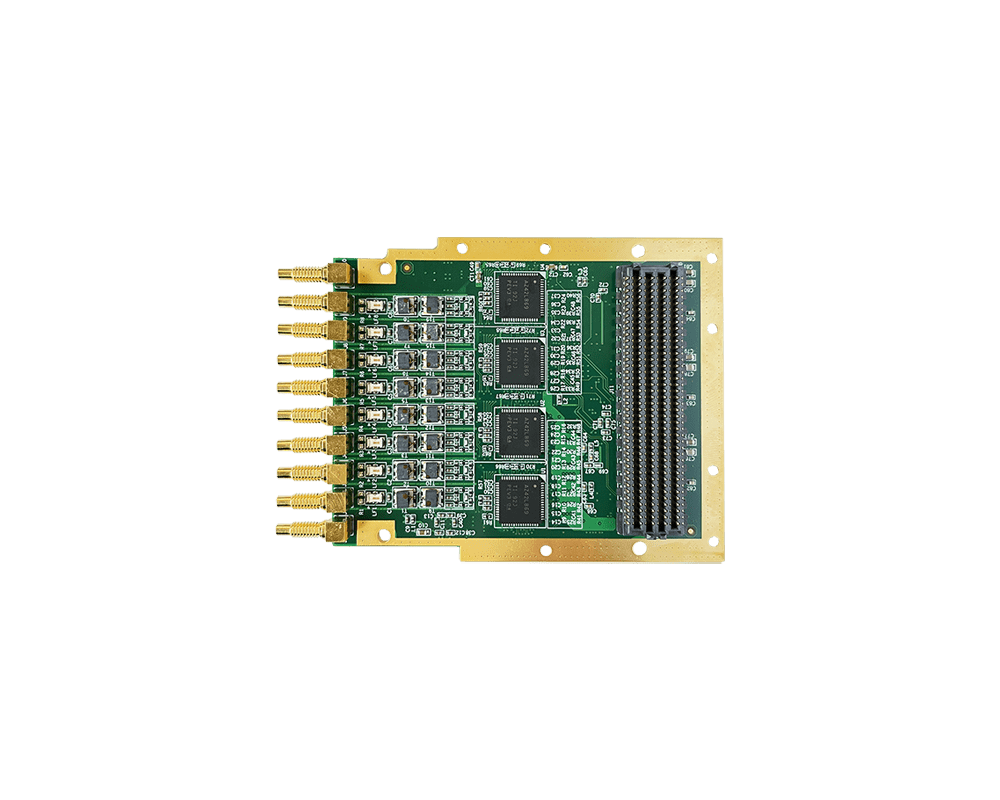

根據(jù)實際系統(tǒng)和算法處理精度要求,硬件系統(tǒng)采用如下設(shè)計:

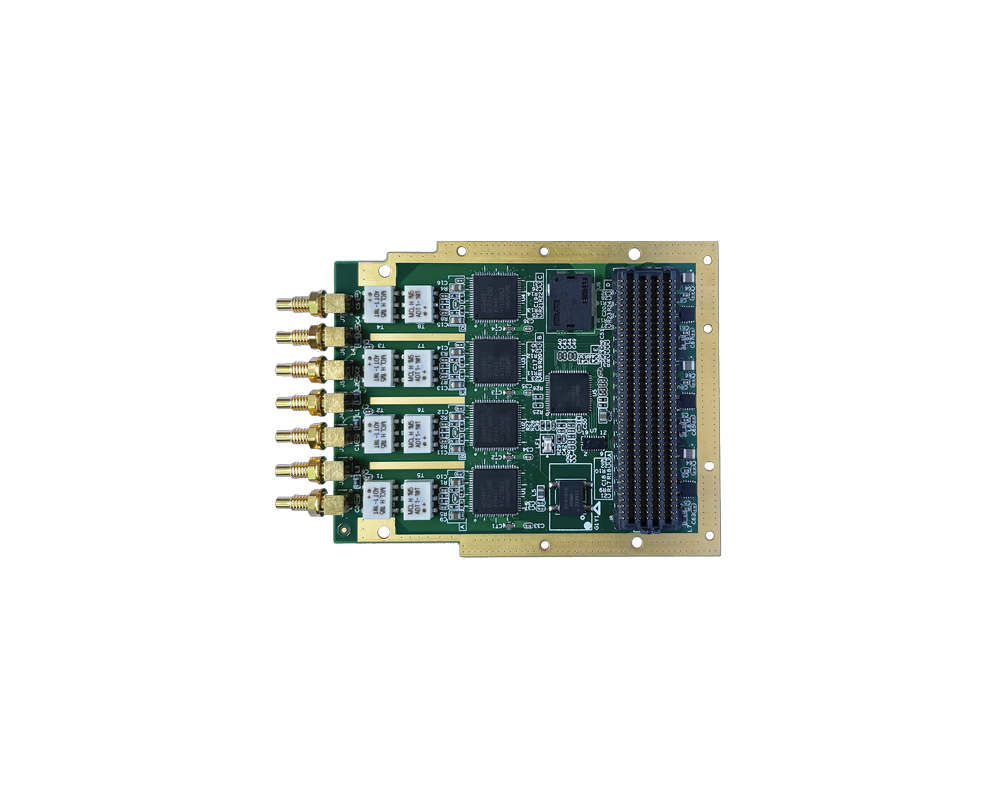

1、10bit2GSPSADC,單通道。

2、低噪聲模擬前端,支持+/-5V~+/-200mV信號輸入,50Ω阻抗BNC接口。

3、板載128MBDDR2內(nèi)存。

4、16個可編程GPIO,可用于系統(tǒng)控制。

5、高穩(wěn)定度,超低低抖動時鐘發(fā)生器。

6、低噪聲電源設(shè)計。

7、LED顯示,指示含有畸變信號的數(shù)量和狀態(tài)。

8、FPGA實現(xiàn)實時信號特征檢測算法功能。

9、USB2.0接口,用戶可以通過USB進行參數(shù)配置以及接收計算結(jié)果。

10、寬溫設(shè)計-20℃~+90℃

11、供電需求,單電源12DC輸入,1A電流。

12、外形尺寸:220mmX90mm

二、系統(tǒng)整體框圖如下:

三、信號的檢測算法:

設(shè)計思想:我們根據(jù)不同的波形曲線進行實時特征統(tǒng)計,提取曲線的特征點,在找到特征點的關(guān)鍵點的性質(zhì),來分析有無畸變情況。

目前特征點的條件定為如下幾點:

特征點由三部分組成

a.一階導(dǎo)數(shù)的零點

b.二階導(dǎo)數(shù)的零點

c.函數(shù)本身的極值點

判決方法為這些特征點的特性變化:

1.計算相鄰特征點的方向向量

2.計算相鄰向量改變角度值

3.相鄰特征點向量方向轉(zhuǎn)變角度閾值,超過該閾值,則認為曲線有可觀測到的變動

判決畸變的規(guī)則:

若輸入序列開始為負值,則找到序列第2個正值(連續(xù)2個為正)再開始判斷

1.若此后序列值符號變化為正(至少再有1個點為正)->負,則判斷存在畸變(曲線出現(xiàn)內(nèi)凹)

2.滿足連續(xù)3個點值為正,且數(shù)值變化小于中間值的25%,則判斷存在畸變(畸變形狀近似直線)

3.滿足連續(xù)5個點值為正,且數(shù)值均小于一個閾值K_TH(較小的數(shù)),則判斷存在畸變(畸變形狀近似直線)

4.滿足一階導(dǎo)數(shù)存在2個以上的較大峰值(大于平均正值斜率均值1.5倍),且峰值大于兩峰之間的斜率均值2倍以上,則存在畸變(曲線部分外凸)

這些規(guī)則分別判定有尖的毛刺,有直線變化以及外凸等情況。該算法架構(gòu)大的好處是可以根據(jù)實際情況增加判決規(guī)則。

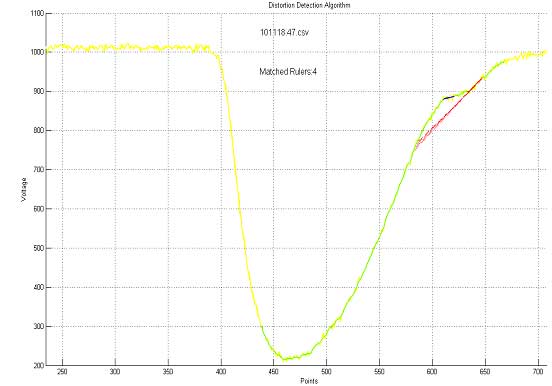

典型數(shù)據(jù)測試測試結(jié)果:

對于典型的畸變信號,順利檢測出畸變量=25。

對于典型的本底信號,畸變量=0。

對于較小的畸變,畸變量=4。

附錄:

高速采集卡的挑戰(zhàn)

為了準確的采集,采集系統(tǒng)的信噪比SNR必須得到保證。影響采集精度的主要要素有以下幾點:

1、量化誤差。

2、lClockjitter和ADCjitter。

3、數(shù)字以及電源干擾

量化精度的提高:

對于量化誤差對采集系統(tǒng)的影響,我們在該系統(tǒng)中選用10bit的ADC,理論![]()

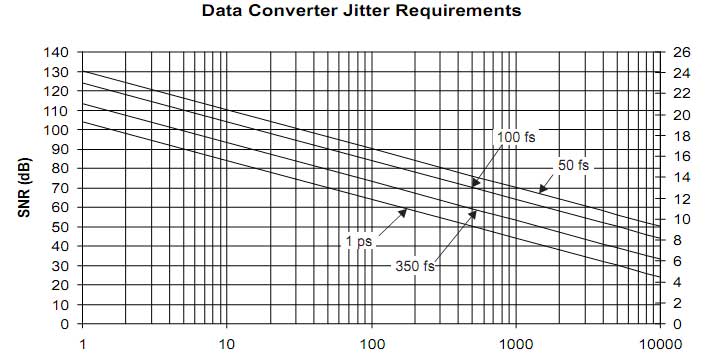

Clockjitter的消除:

該方案中采用溫度補償晶體TCXO以及業(yè)內(nèi)頂級的JittercleaningCLKGenerator芯片來保證clock的穩(wěn)定性,Clockjitter的消除以及極低的Phasenoise。

在寬溫工作環(huán)境下,普通的晶體隨著工作溫度的變化,晶體的穩(wěn)定度和頻率都會發(fā)生改變,為解決該問題,我們選用超低相位噪聲的晶體。

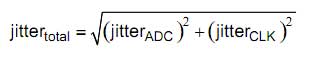

對于時鐘芯片的選擇,也是基于同樣的考慮,集成高精度高穩(wěn)定的VCO,具有Jittercleaning功能和clkphaseadj功能。通常,jitter由ADC本身的jitter和CLKjitter組成,各自的RMS再組成總jitter的RMS:

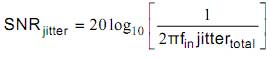

總jitter的RMS會在采集系統(tǒng)中產(chǎn)生白噪聲,其關(guān)系如下:

采集系統(tǒng)的總=![]()

采用本時鐘解決方案,其總的clockjitter在系統(tǒng)中完全能做到<1ps。在忽略信號noise,dnl等情況下,fin和clockjitter有如下關(guān)系:

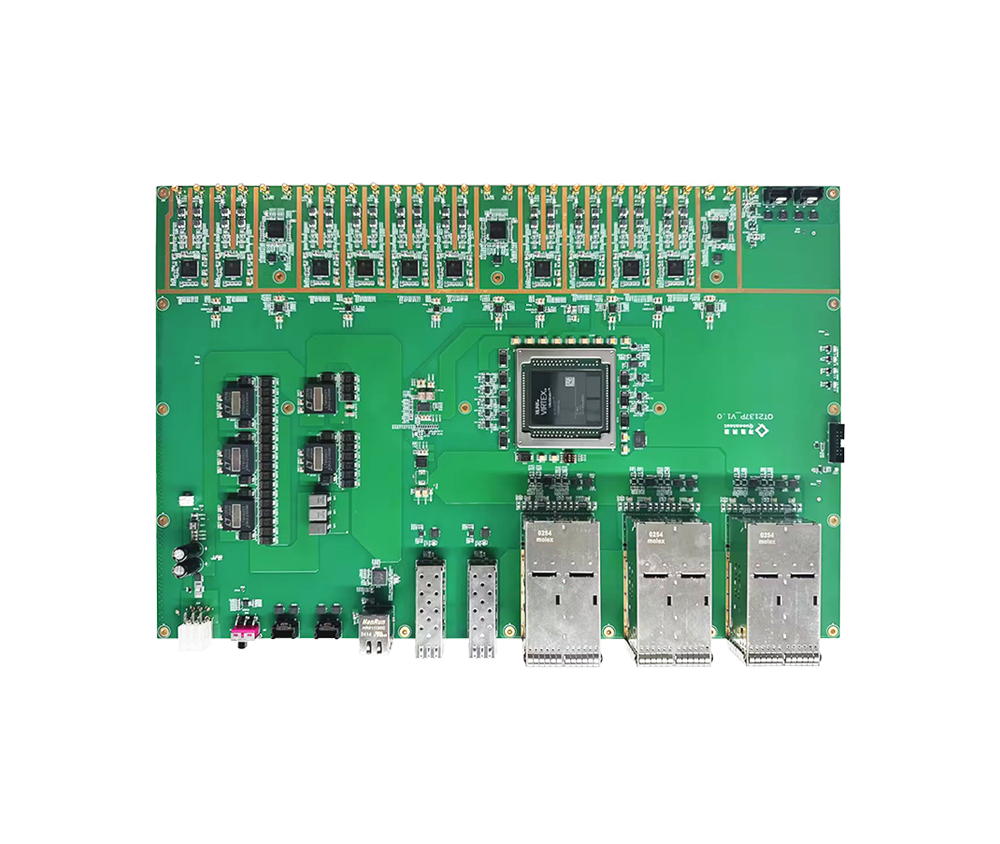

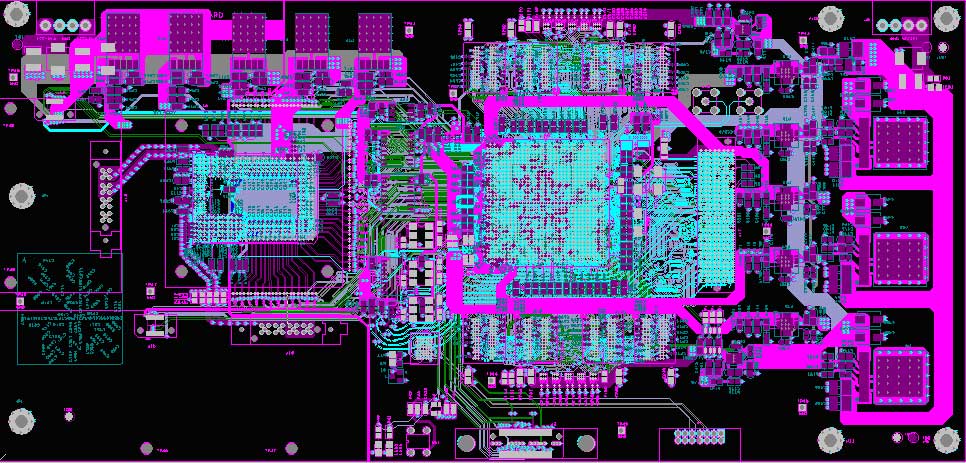

合理的高速數(shù)模混合PCB設(shè)計,充分論證信號完整性和電源完整性,PCB版圖如下:

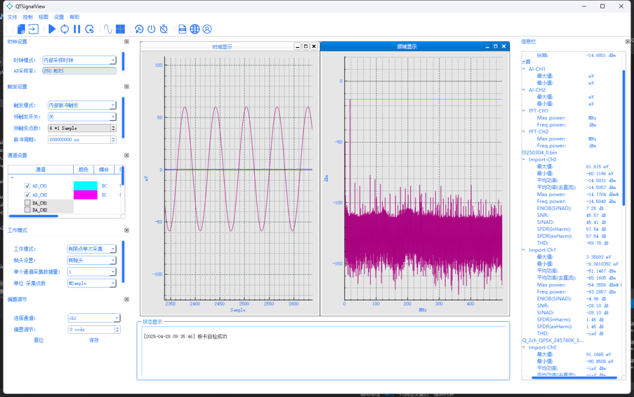

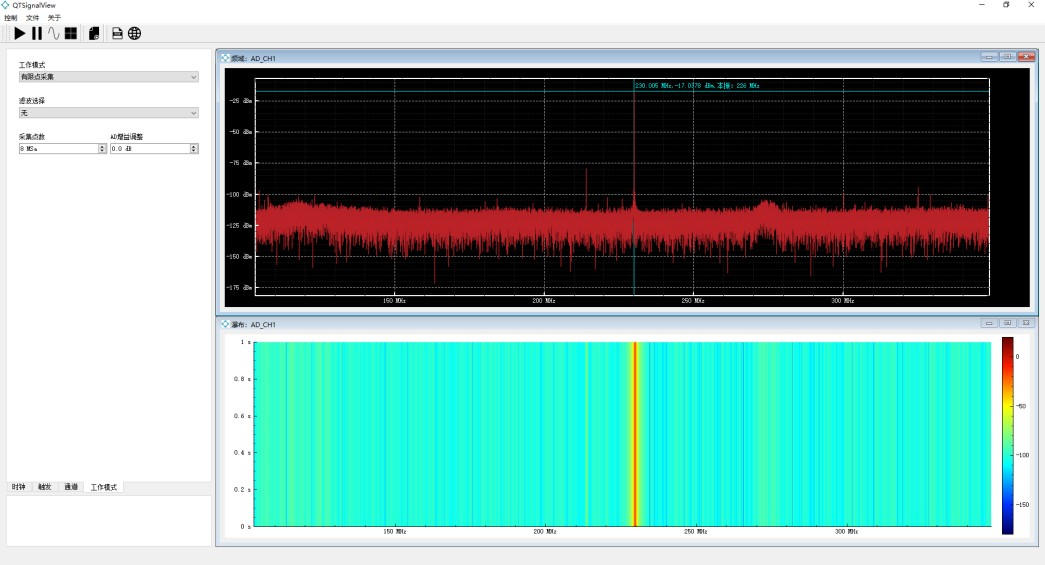

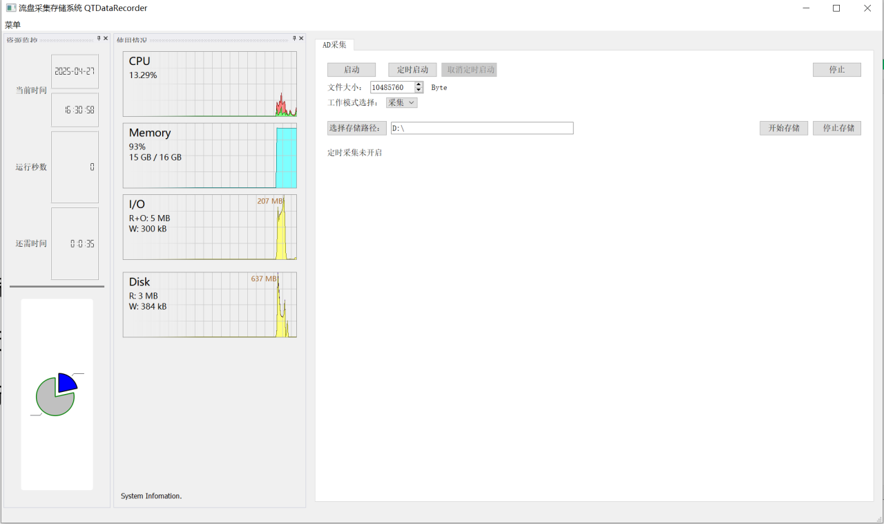

采集測試方案以及ADC芯片性能力指標

1.ADC性能測試

ADC模塊的測試:

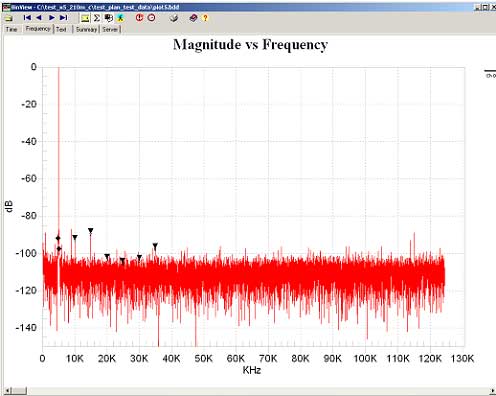

使用AgilentE8663DRF信號發(fā)生器,主要發(fā)生單頻的sine信號,通過窄帶濾波器,保證sine的“純凈”。信號幅度為+/-1V輸出,保證ADC輸入的滿幅度。

信號通過ADC采集后進入PC并存儲,通過測試軟件進行數(shù)據(jù)處理。

關(guān)于ADC采集數(shù)據(jù)的處理及計算方法:

Data輸入可以選取多個點(如4K-16K),同hanningwindow進行卷積,防止矩形窗引起的Gibbs現(xiàn)象。

卷積后的信號進行FFT,得到頻譜數(shù)據(jù)。這是為了測試數(shù)據(jù)的準確性,可以多采集幾次進行譜平均,得到更準確的譜數(shù)據(jù)。

ADC性能的測試:

我們可以在頻譜中找到輸入sine的基波信號,以及除去其高次諧波的噪聲能量,得到SNR的指標:

SNR=20*log([Fundamental]/SQRT(SUM(SQR([Noise]))))

以及

SFDR=20*log([Fundamental]/[HighestSpurious])

SINAD=20*log([Fundamental]/SQRT(SUM(SQR([Noise+Harmonics]))))

ENOB=(SINAD–1.76)/6.02

根據(jù)如上測試方法,本系統(tǒng)的采集性能達到如下性能指標:

Fs=2Gsps

Fin=500MHz

SNR:42dBc

ENOB:7bit

THD:45dBc

SFDR:48dBc