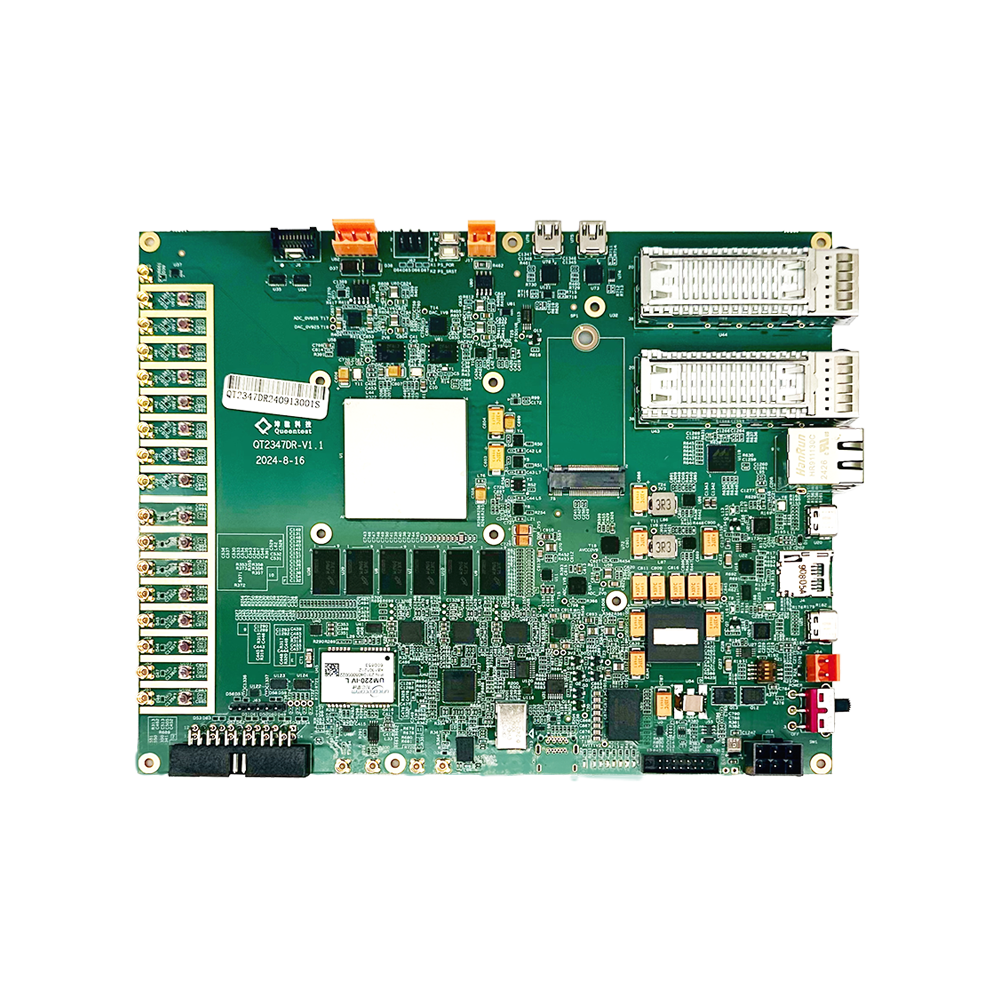

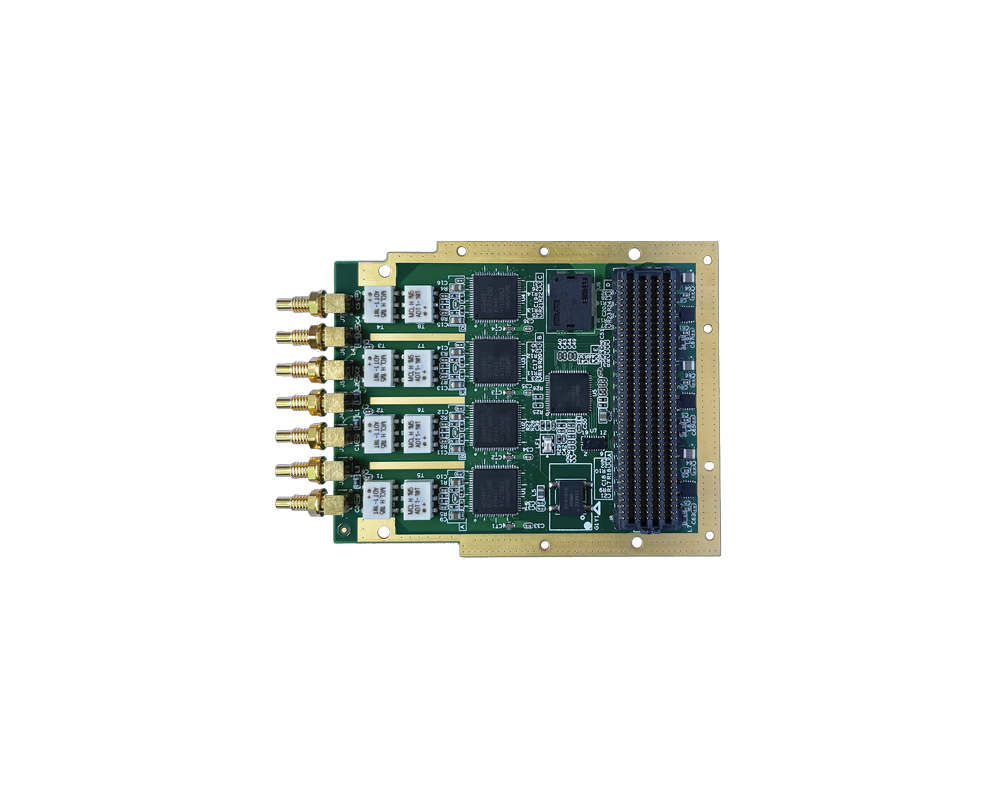

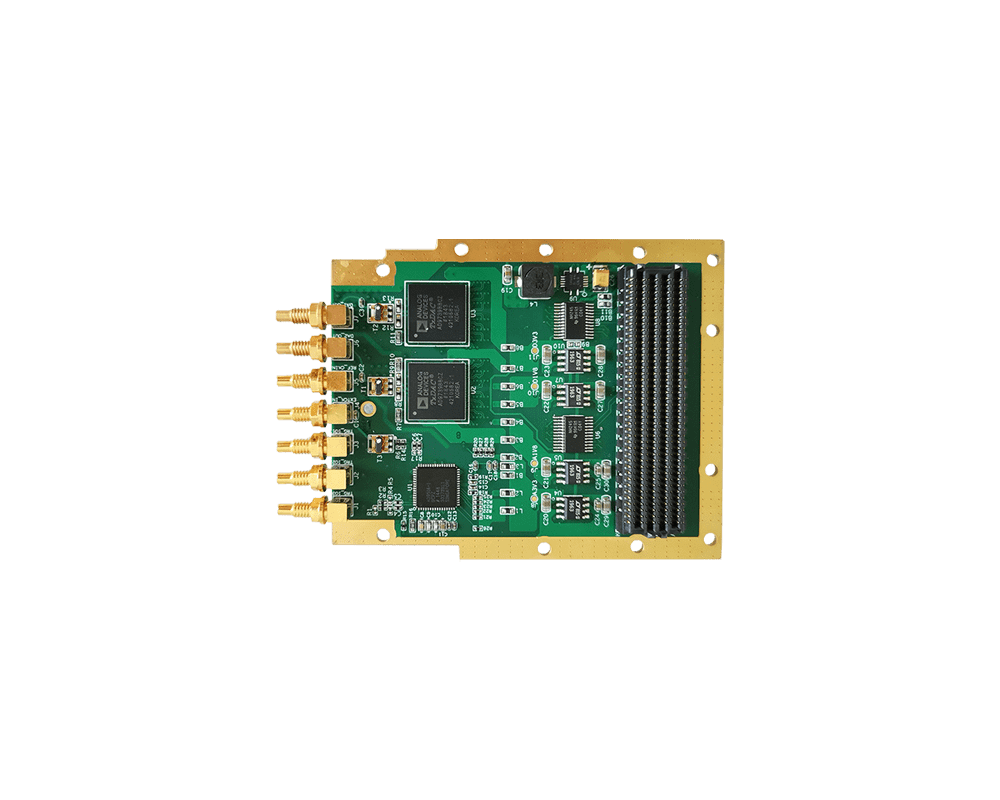

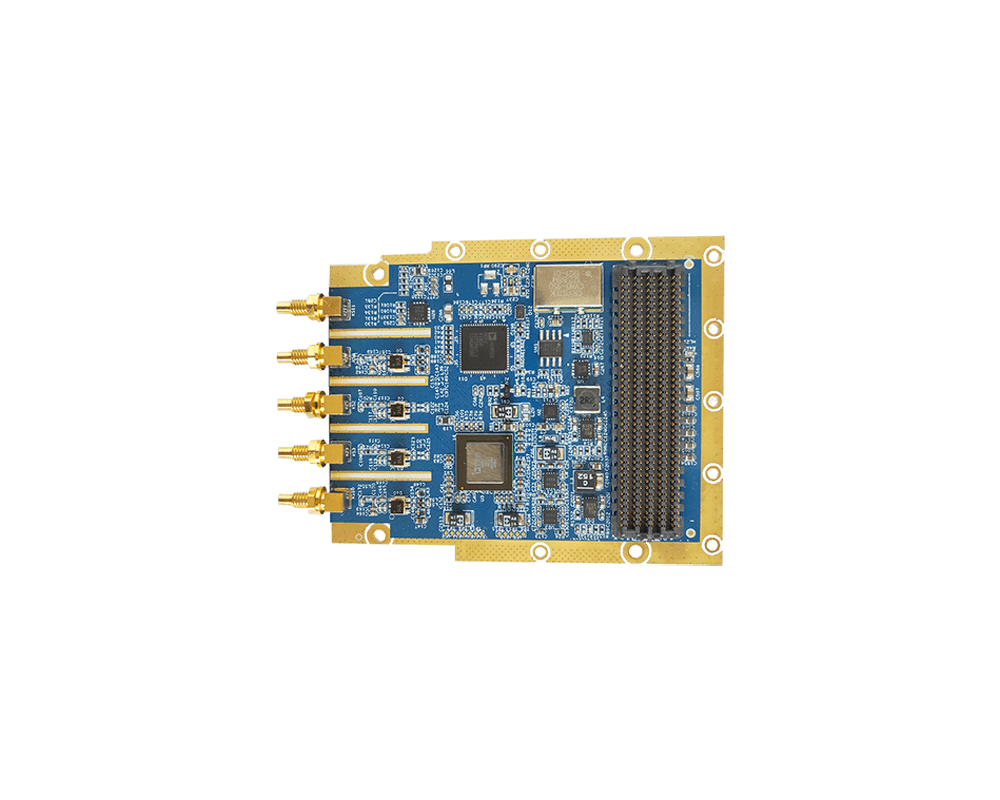

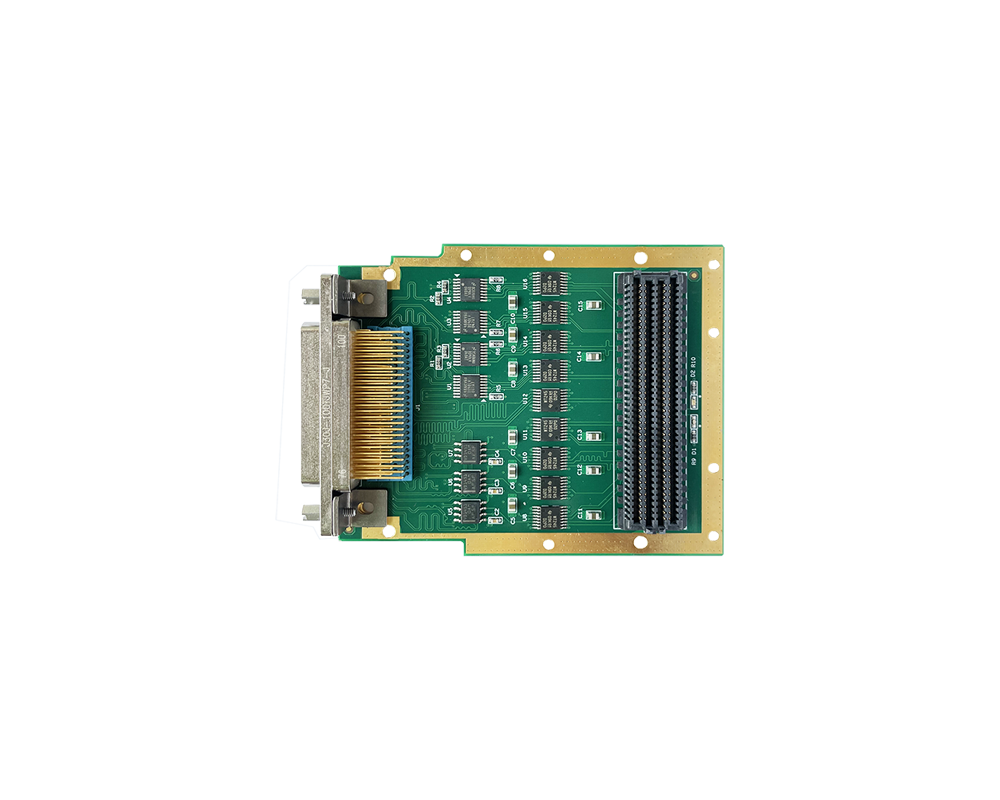

在高速數(shù)據(jù)采集卡的設(shè)計過程中要涉及到對DDR2、DDR3的讀寫測試問題,在文即對測試過程做個小小的總線。

首先對生成的MIGDDR2的example中的源代碼進(jìn)行詳細(xì)的閱讀,結(jié)合對sim文件中的sim.do進(jìn)行仿真,從而能夠得到DDR2的時序控制。項目中的DDR2調(diào)用的是IP核,在手冊中給出了DDR2IP核的用戶的端口。這些端口是用來進(jìn)行控制的,從而避免了關(guān)注DDR2的內(nèi)部結(jié)構(gòu),這將大大簡化對DDR2的控制難度。

在編寫DDR2的讀寫測試代碼中,遇到了一個問題:

在仿真中發(fā)現(xiàn)app_af_addr端口給出的地址不能和寫地址使能信號app_af_wren相匹配,在后的仿真中看到第8位傳輸?shù)刂分荒軅鬏斠话耄@就造成了讀寫地址混亂的情況。

起初的代碼如下:

always@(posedgeclk0)begin

if(!rst0)

begin

addr_cnt<=35'd0;

endelseif(addr_cnt==35'd7)

addr_cnt<=35'd0;

elseif(wr_addr_en)

addr_cnt<=addr_cnt+1'b1;

End

對于這個問題考慮的角度是第8位地址數(shù)據(jù)在addr_cnt在系統(tǒng)時鐘clk0的上升沿到來之后,就會立刻將addr_cnt賦值為0,并沒有等待wr_addr_en是否結(jié)束。從而造成了后面地址混亂。解決的方法如下所示:

always@(posedgeclk0)begin

if(!rst0)

begin

addr_cnt<=35'd0;

endelseif(addr_cnt==35'd7&&wr_addr_en==1)

addr_cnt<=35'd0;

elseif(wr_addr_en)

addr_cnt<=addr_cnt+1'b1;

End

這樣就可以將addr_cnt和地址寫使能wr_addr_en相匹配,終得到正確的時序關(guān)系。

造成這種問題的原因:

在編程過程中對時鐘信號的整體把握有欠缺,應(yīng)該對整體的時序有清楚的把握。

為了我們共同的目標(biāo)“做專業(yè)的高速數(shù)據(jù)采集廠商”而共同努力!

關(guān)于坤馳科技:

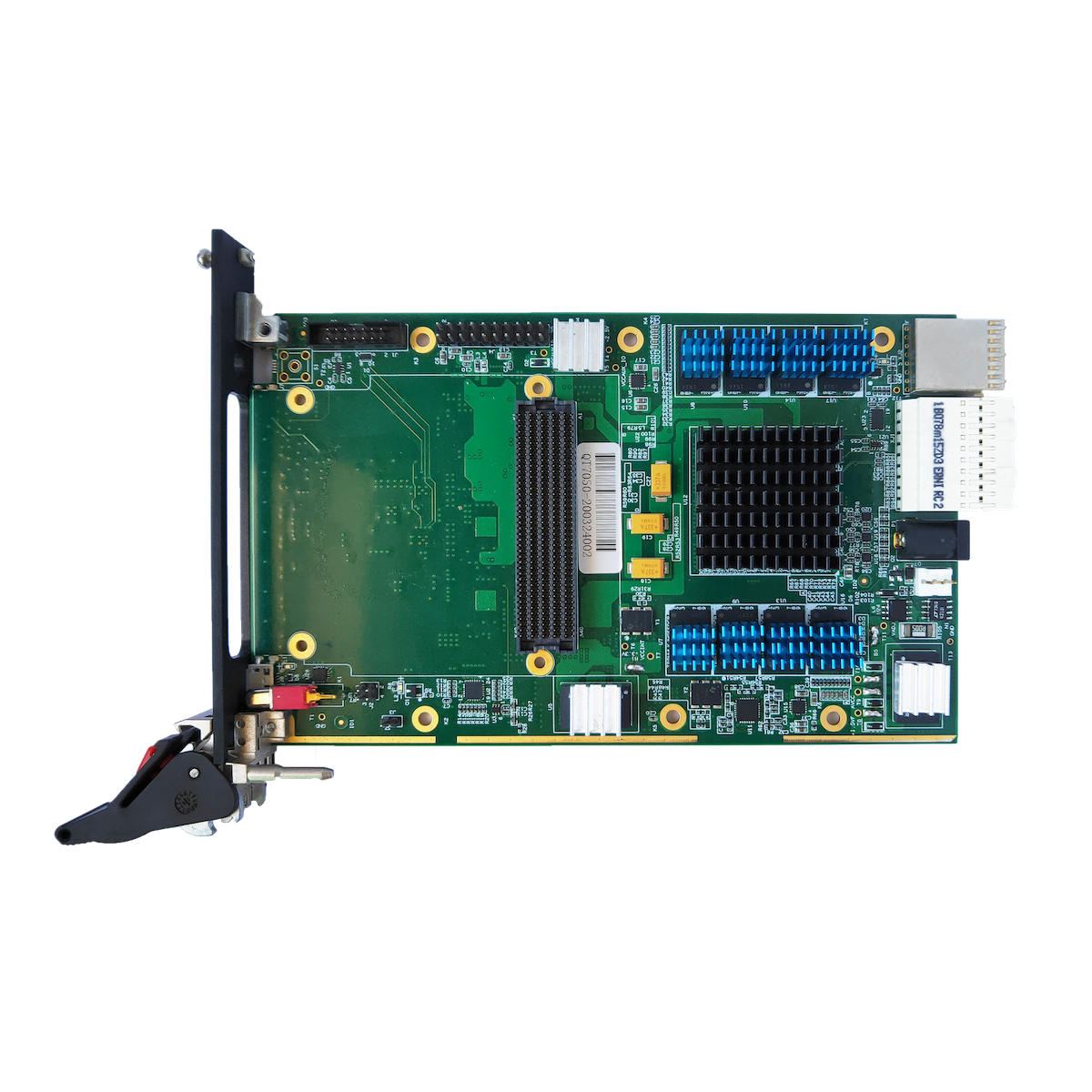

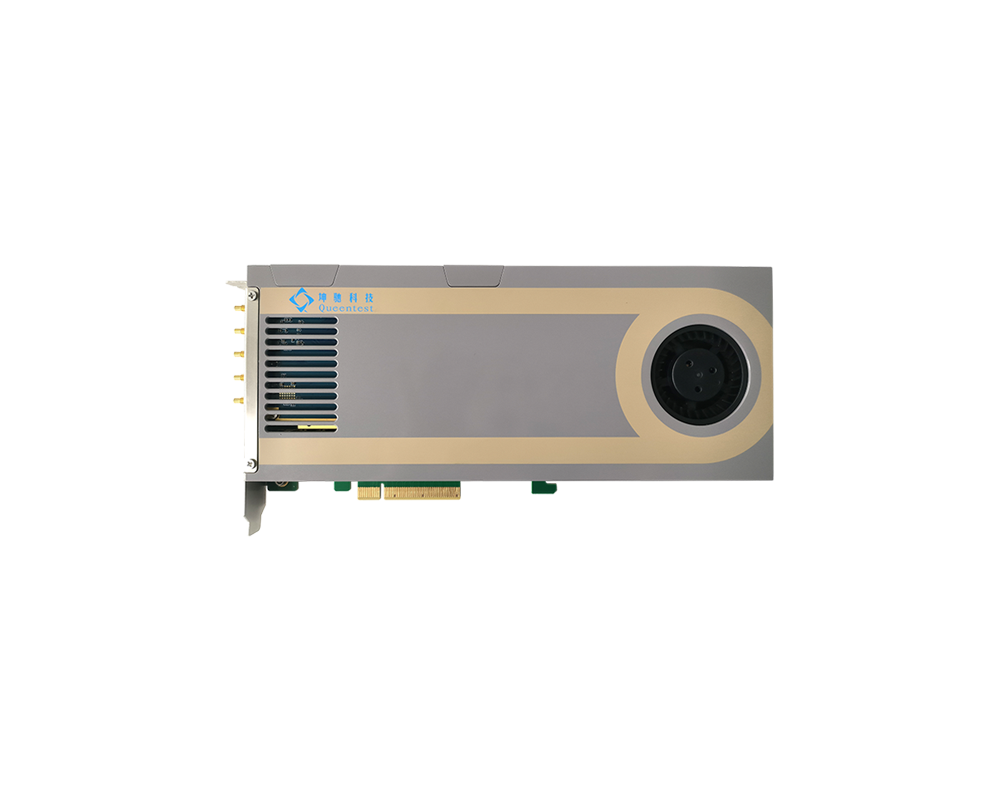

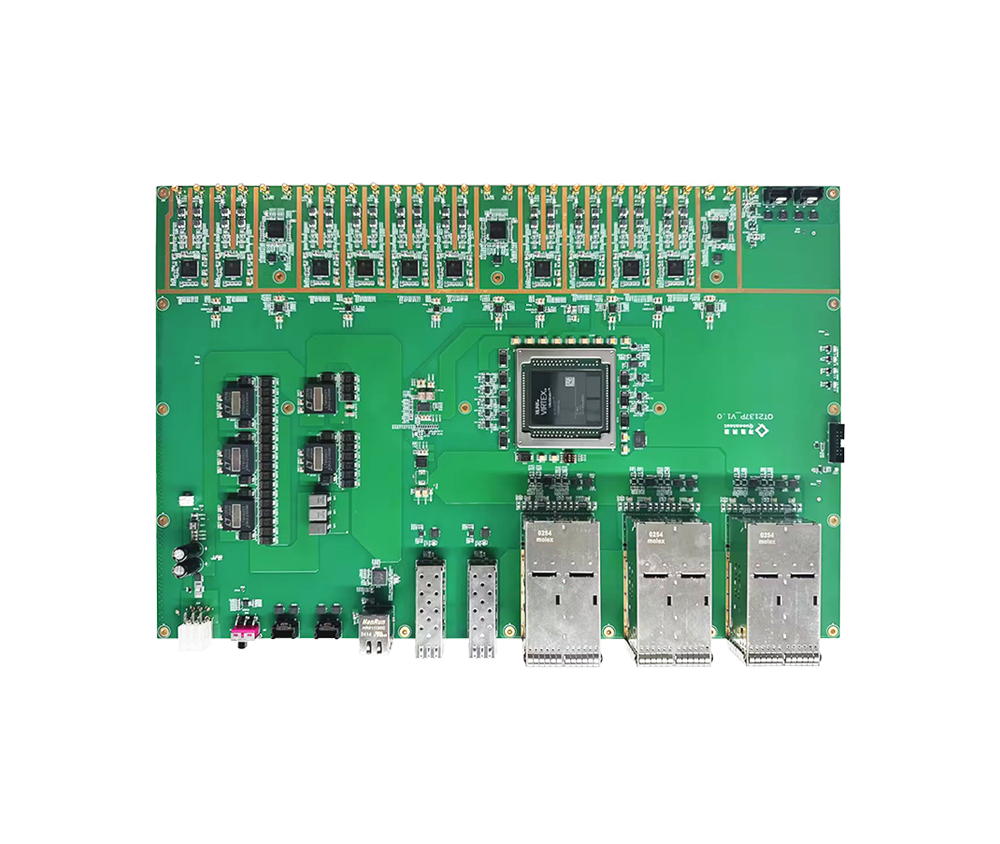

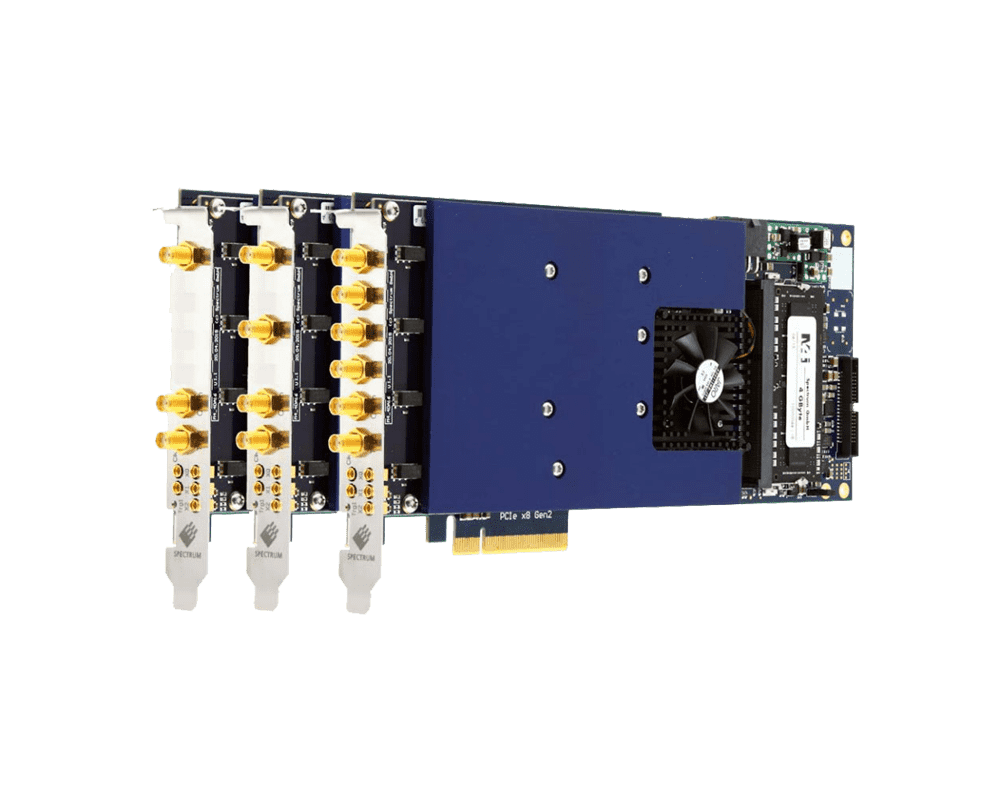

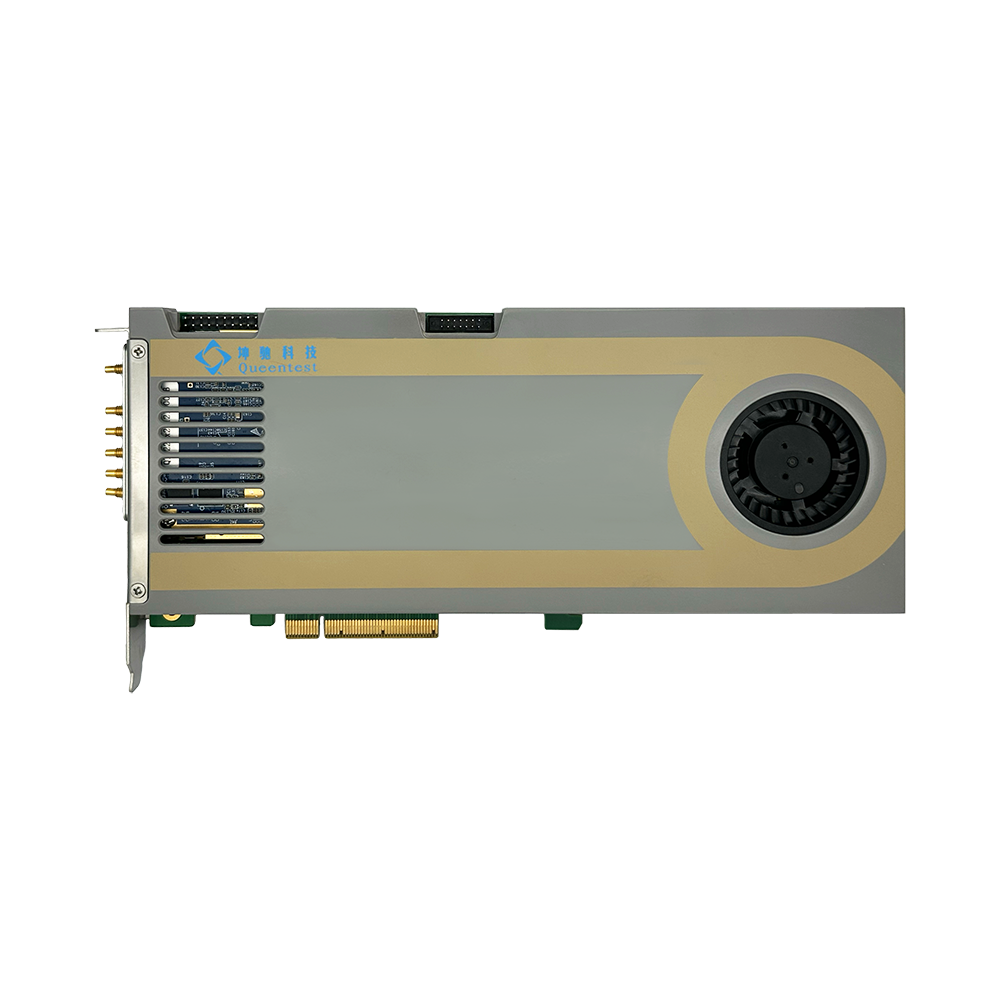

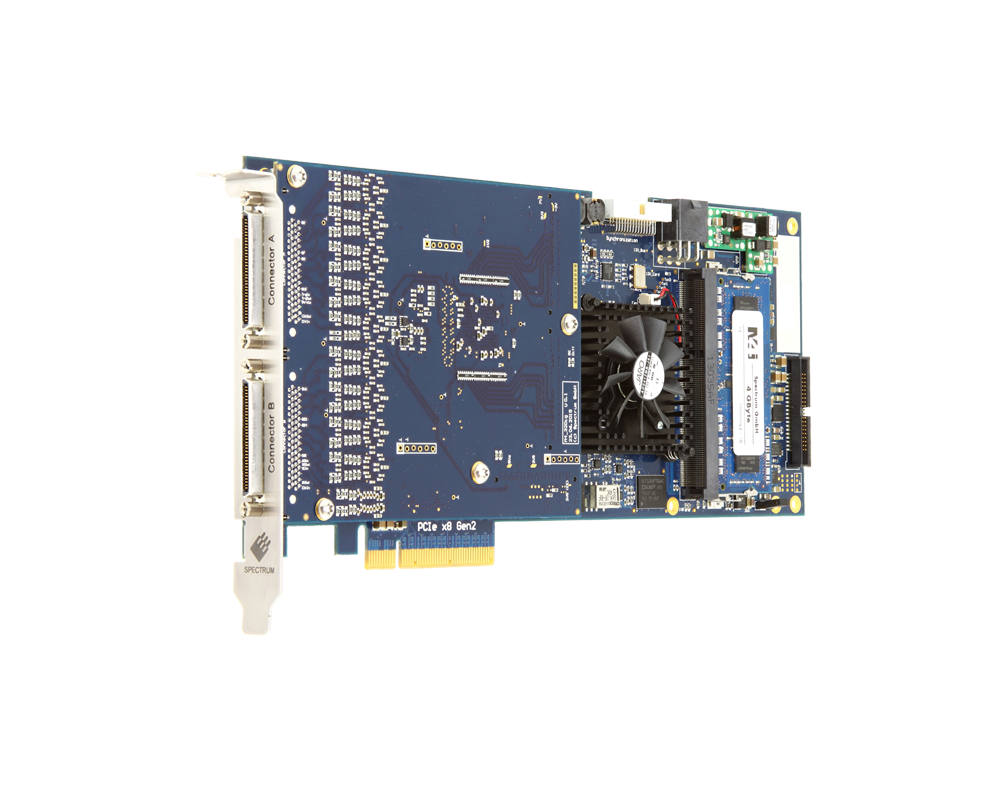

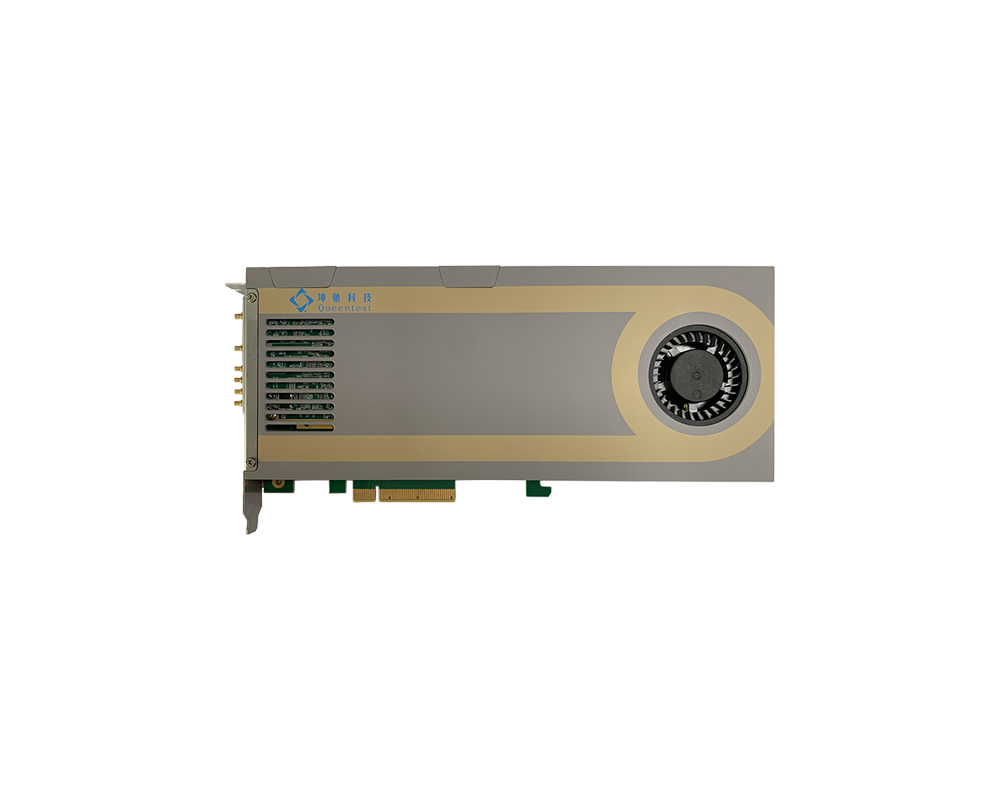

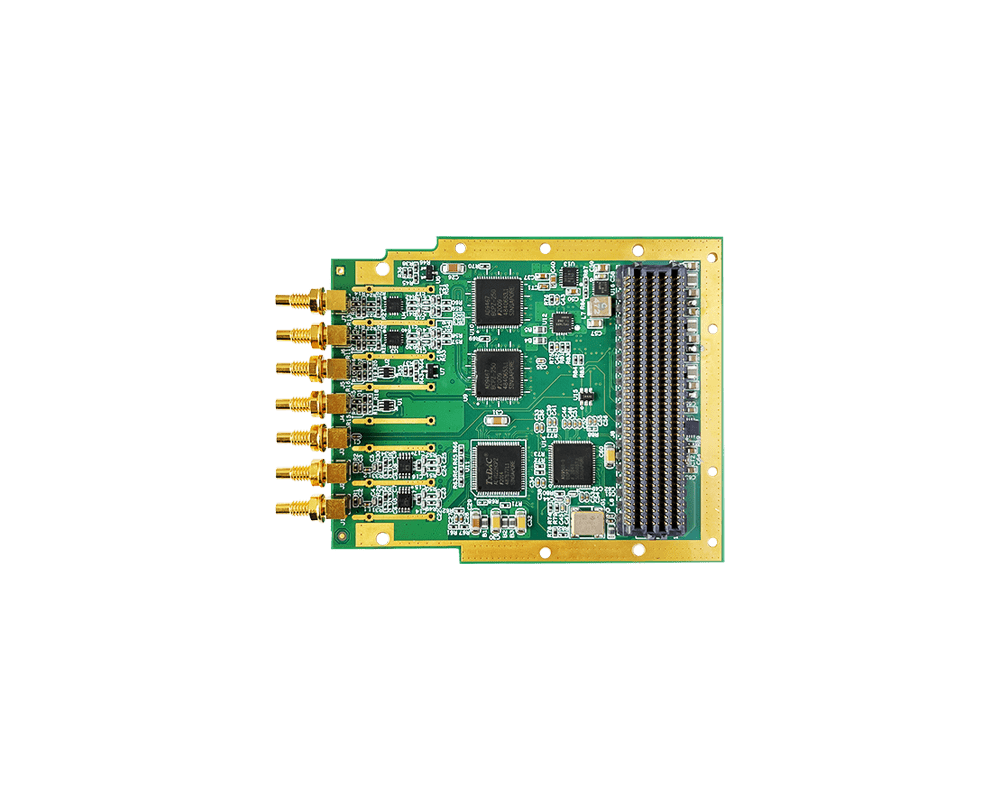

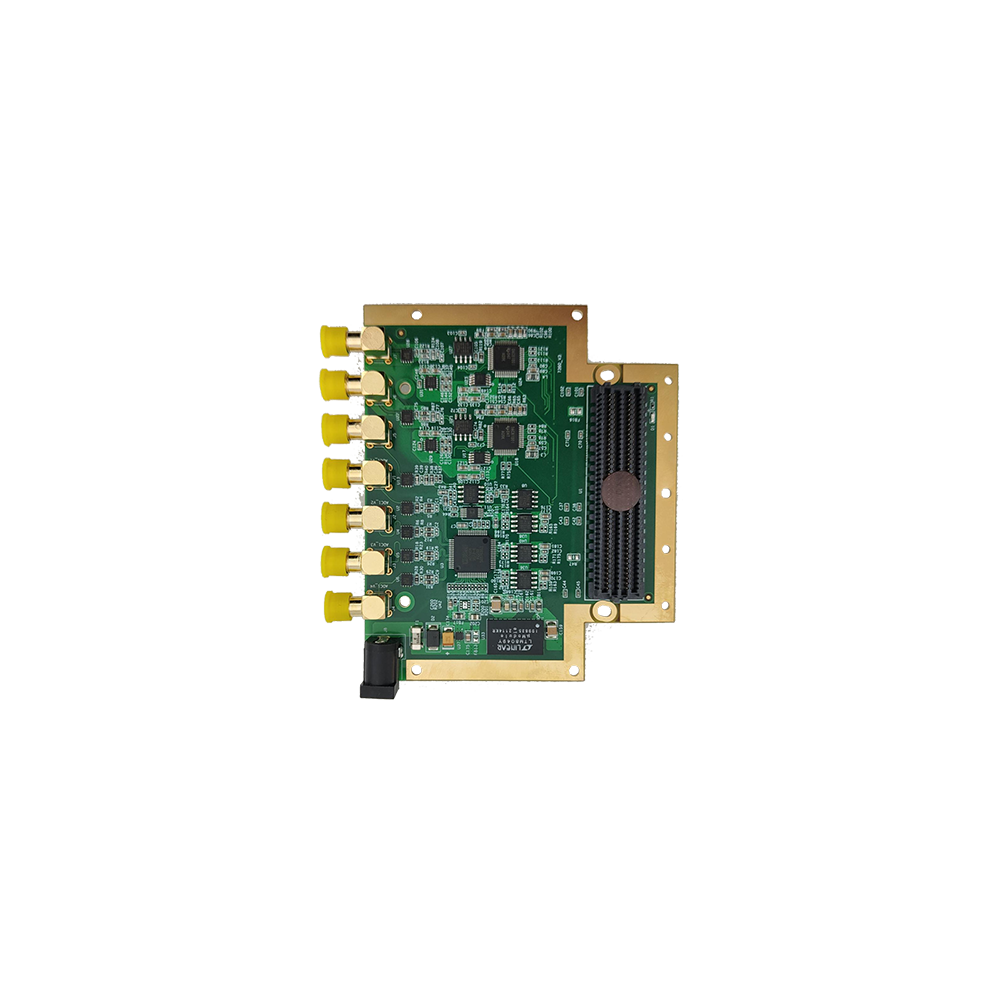

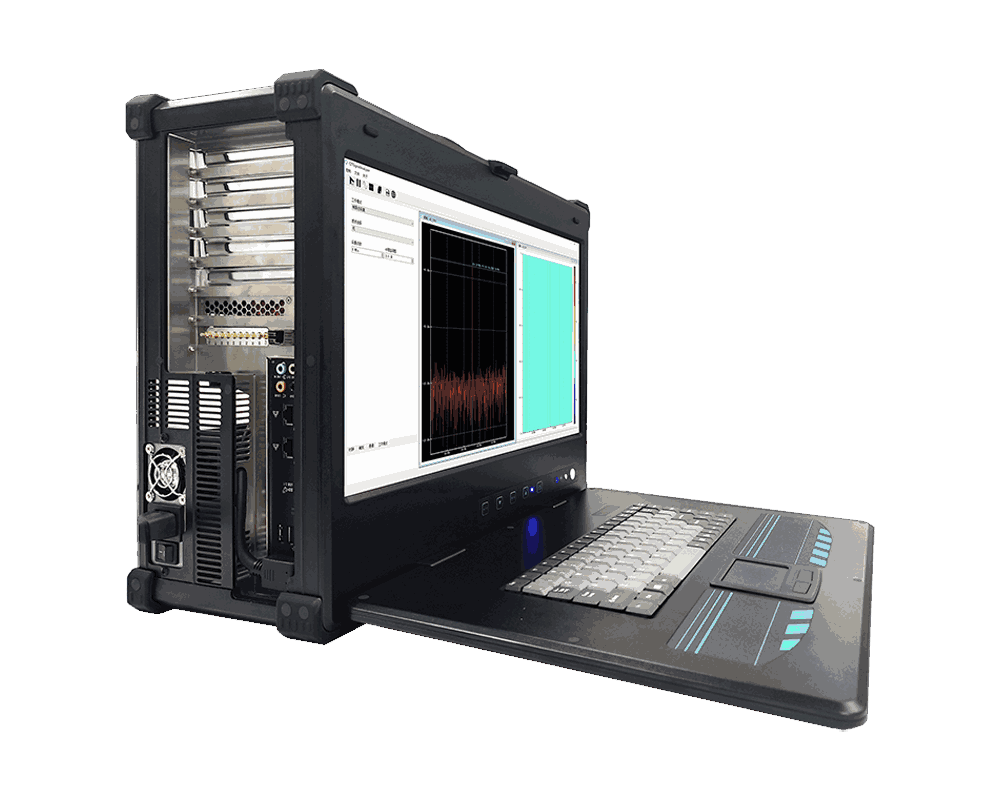

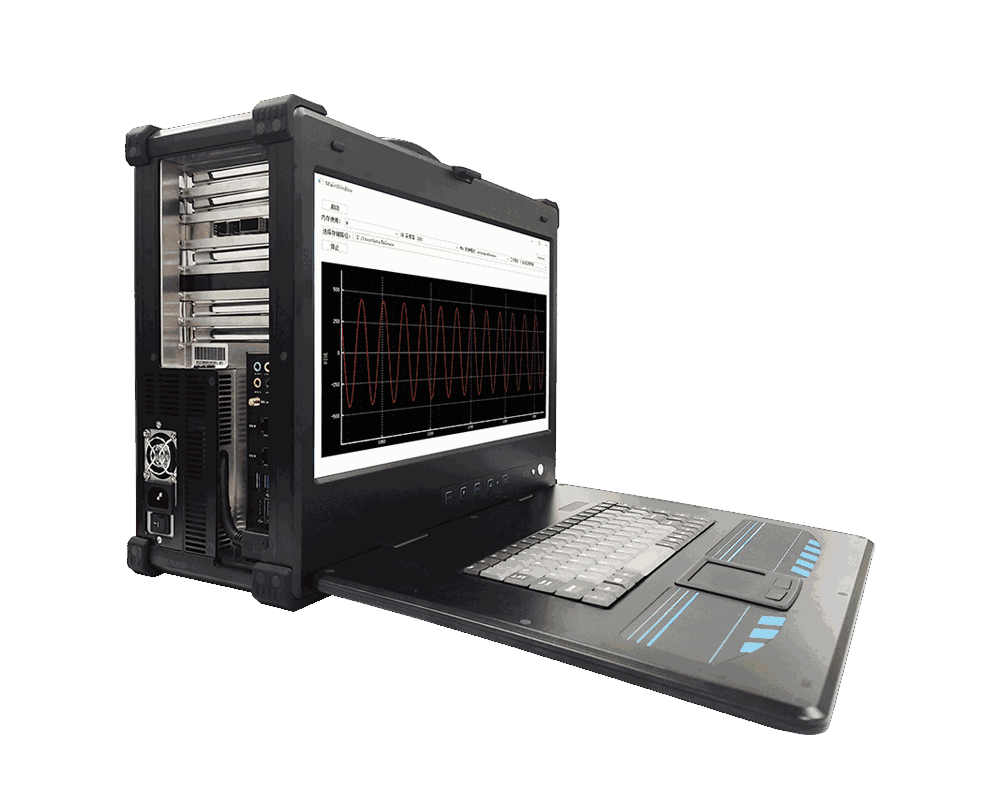

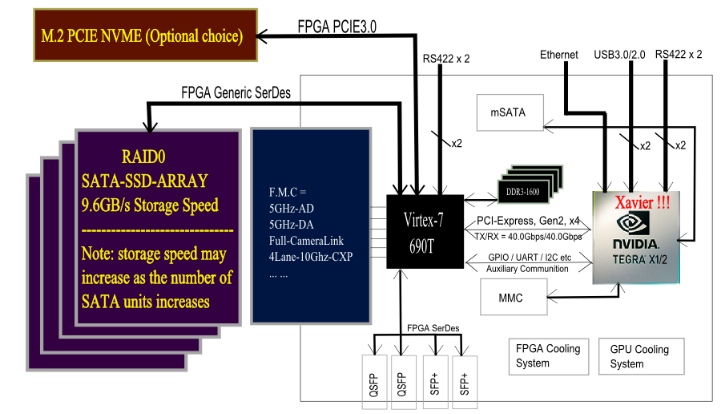

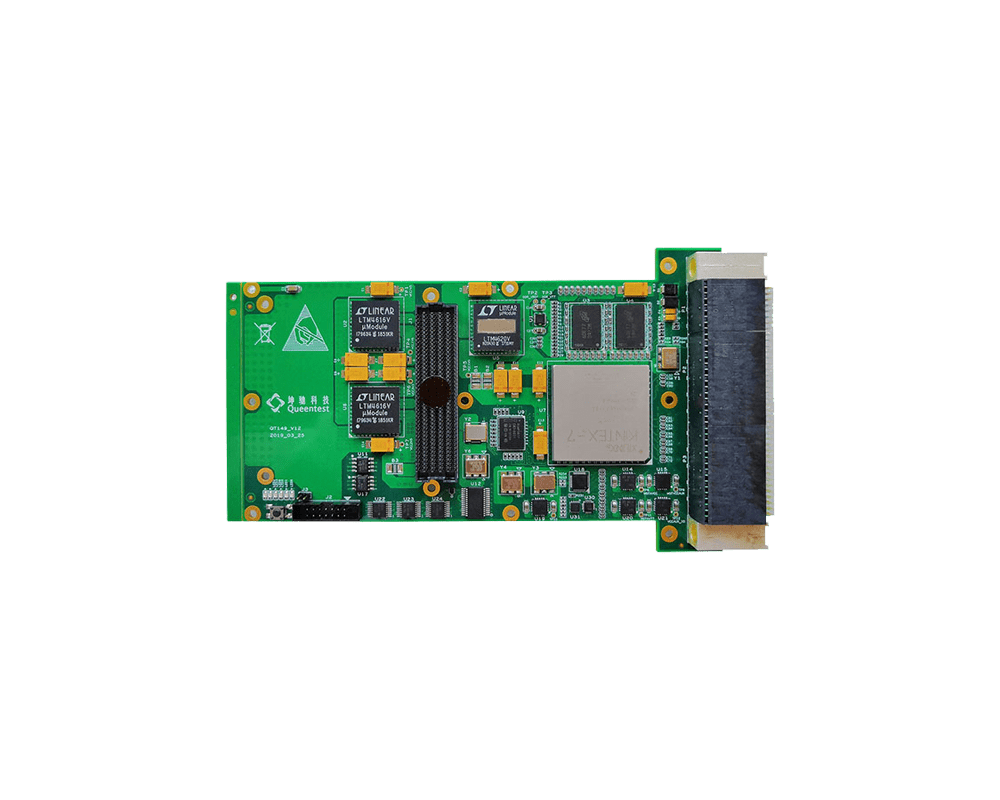

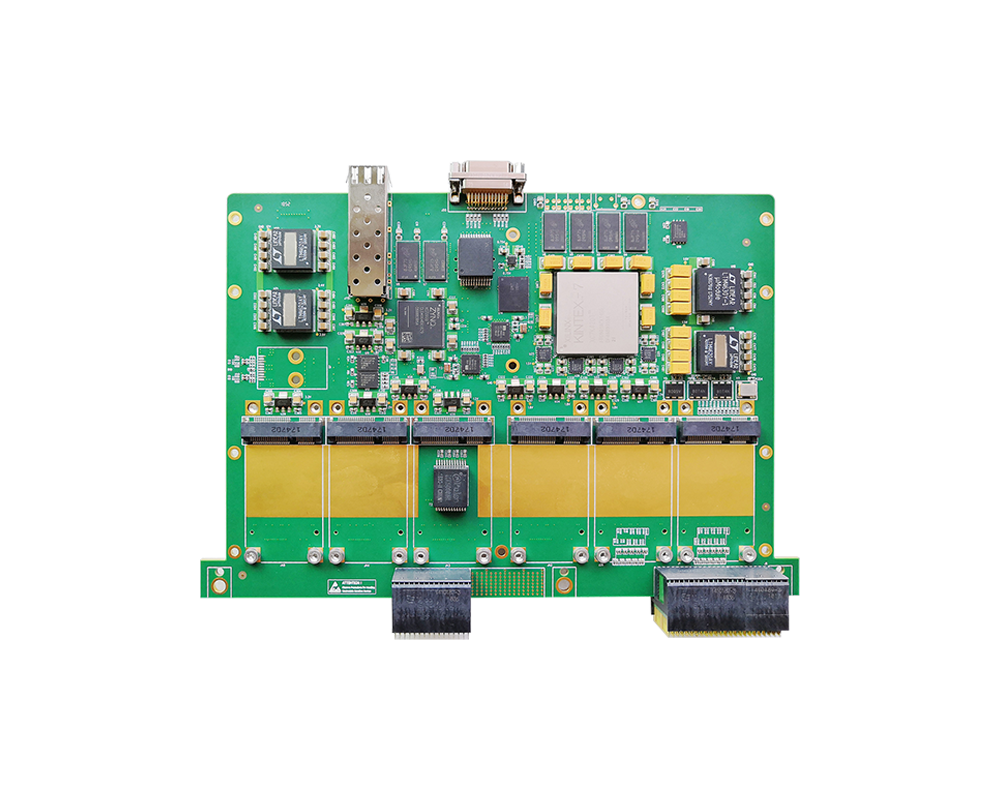

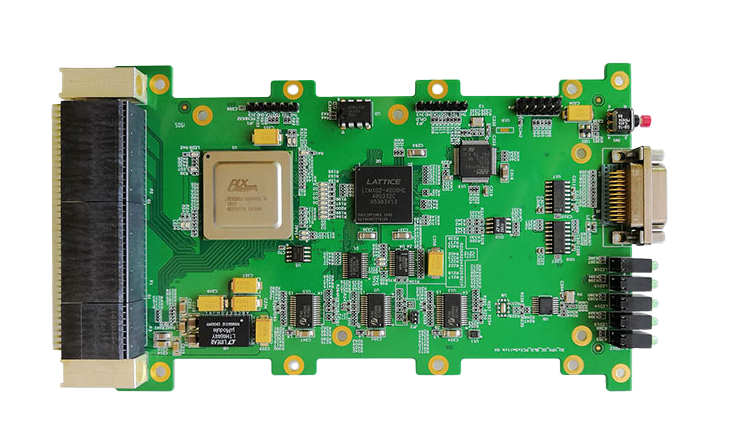

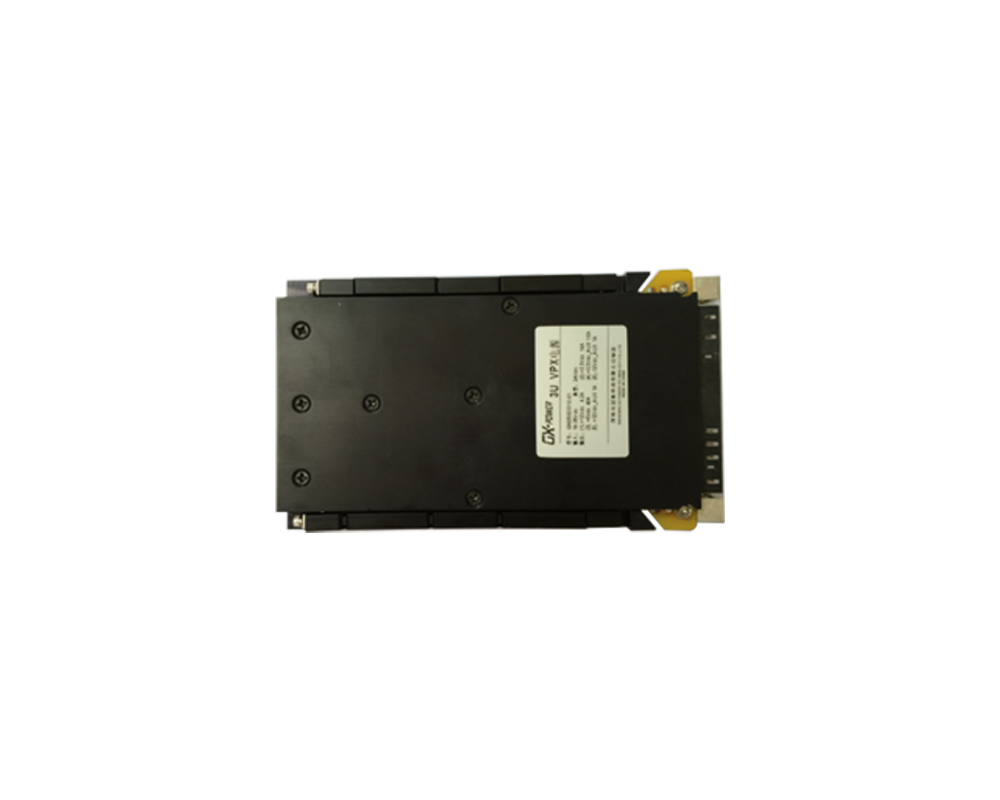

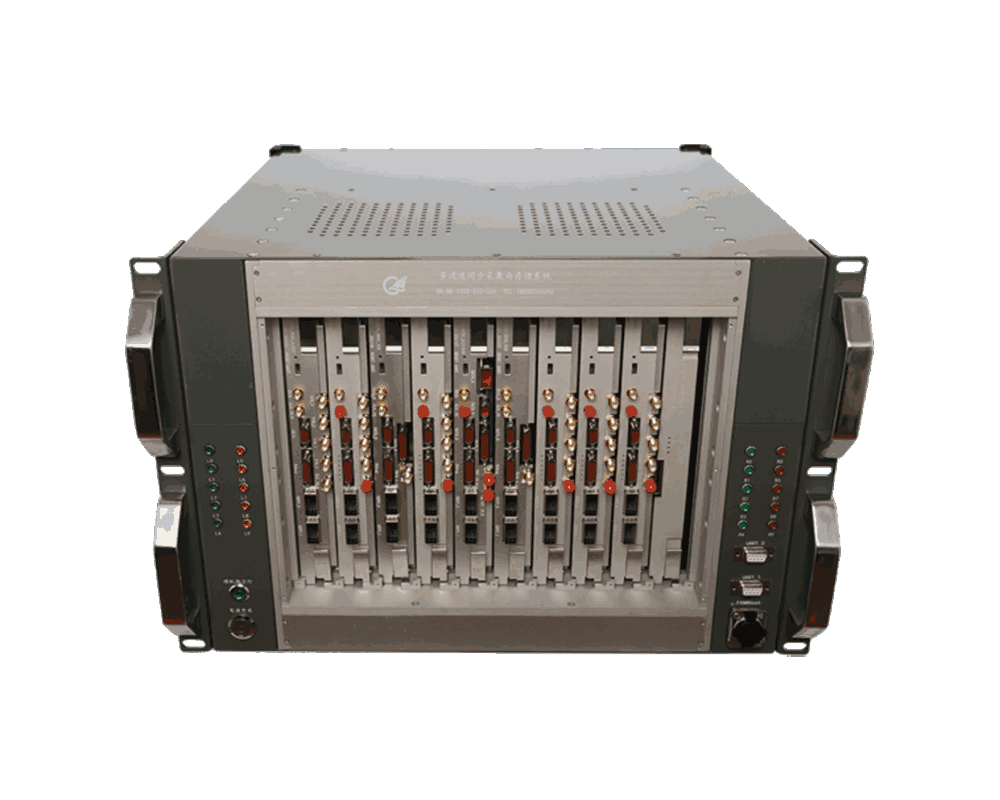

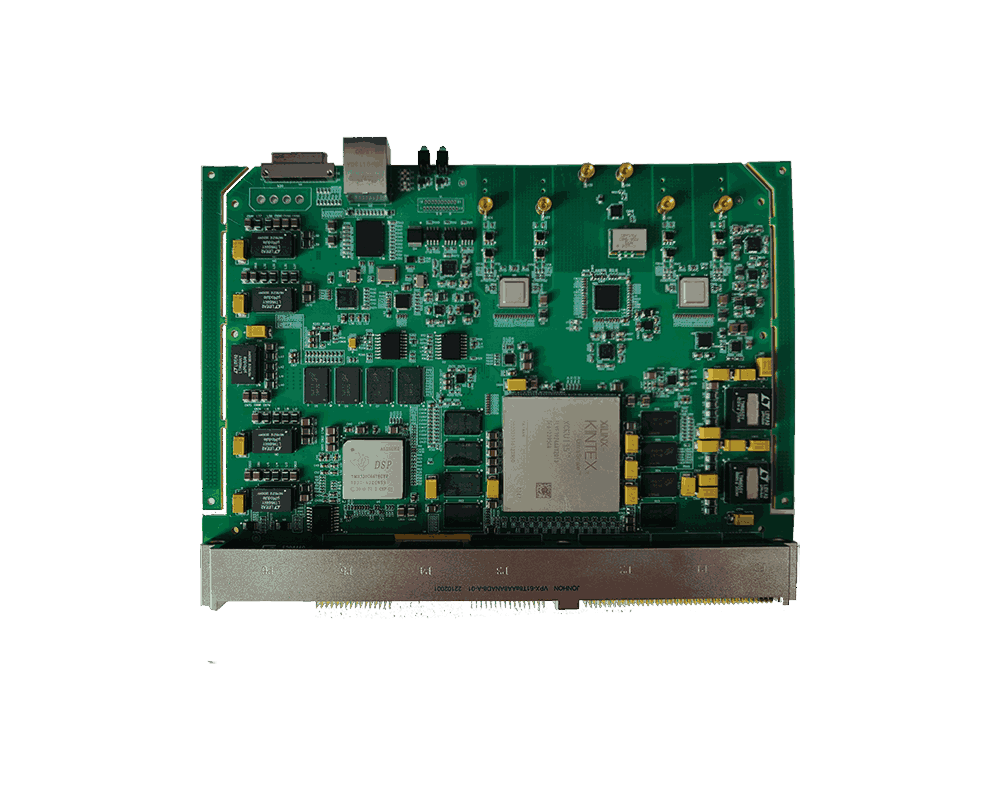

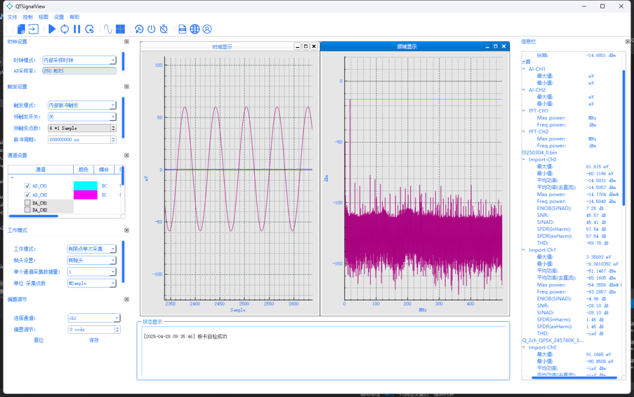

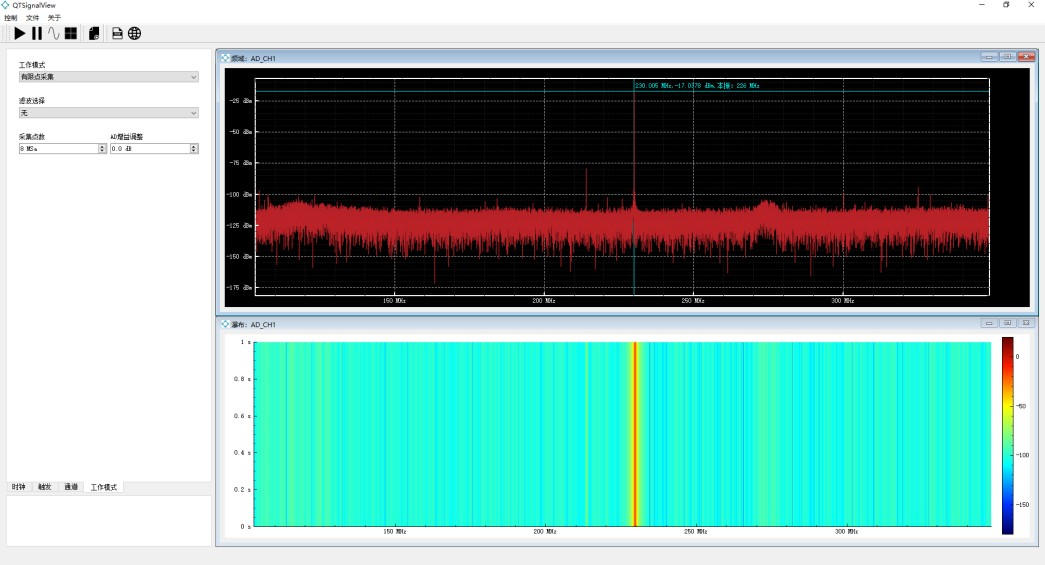

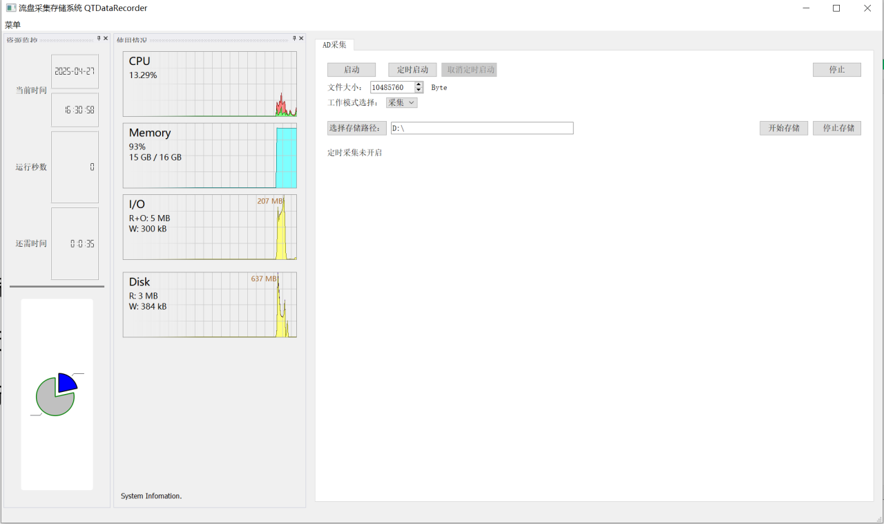

坤馳科技是專注于高速數(shù)據(jù)采集與信號處理、高速數(shù)據(jù)存儲與記錄的高科技公司。坤馳科技為用戶提供成熟的標(biāo)準(zhǔn)高速數(shù)據(jù)采集產(chǎn)品與技術(shù),也可為用戶提供定制化的高速信號采集解決方案。目前坤馳科技服務(wù)過的研究所、科研單位已達(dá)近百家。高速數(shù)據(jù)采集產(chǎn)品線涵蓋PCIExpress、cPCI、PXIe、VPX、USB等總線,包含高速AD、DA平臺、FPGA、DSP處理平臺,SATA/SSD、Flash存儲平臺等。

全國咨詢電話:400-000-4026

公司官方網(wǎng)站:http://www.queentest.cn

官方微博:http://e.weibo.com/queentest

官方微信:queentest或掃描: