近在做DDR3的邏輯開發。由于需要測試電路板上的DDR3是不是正確,需要先用MIG核生成的 example design 來測試一下。但是 example design是需要修改一下的。

(1)將example design 中的 系統時鐘sys_clk 和iodelay 參考時鐘clk_ref 注釋掉,引入板上125MHz差分時鐘 clk_125M_p (clk_125M_n)。

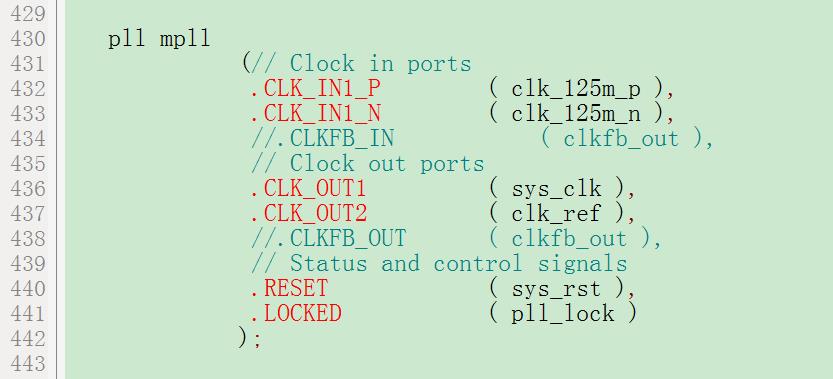

(2)125MHz板上時鐘 clk_250M_p(clk_250M_n)經過 PLL產生出500MHz的sys_clk時鐘和300MHz的iodelay 參考時鐘。

(3)將系統復位 sys_rst 注釋掉,引入系統復位 sys_rst_n;sys_rst_n為低電平復位,而DDR3 example design 中的sys_rst為高電平復位。因此 sys_rst_n需要取反。

(4)修改UCF中的相應管腳約束。

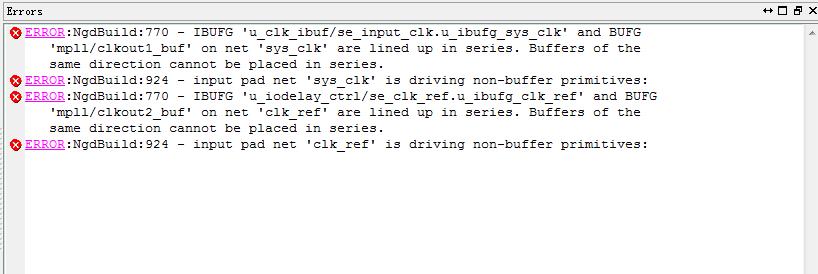

按照上述步驟修改之后,在“translate”時出現錯誤。如下圖:

大概意思是說sys_clk 上有兩個BUFG串聯,clk_ref上也有兩個BUFG串聯。于是查找程序發現程序如下:

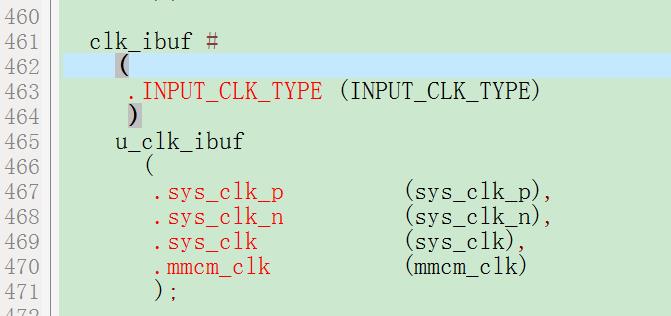

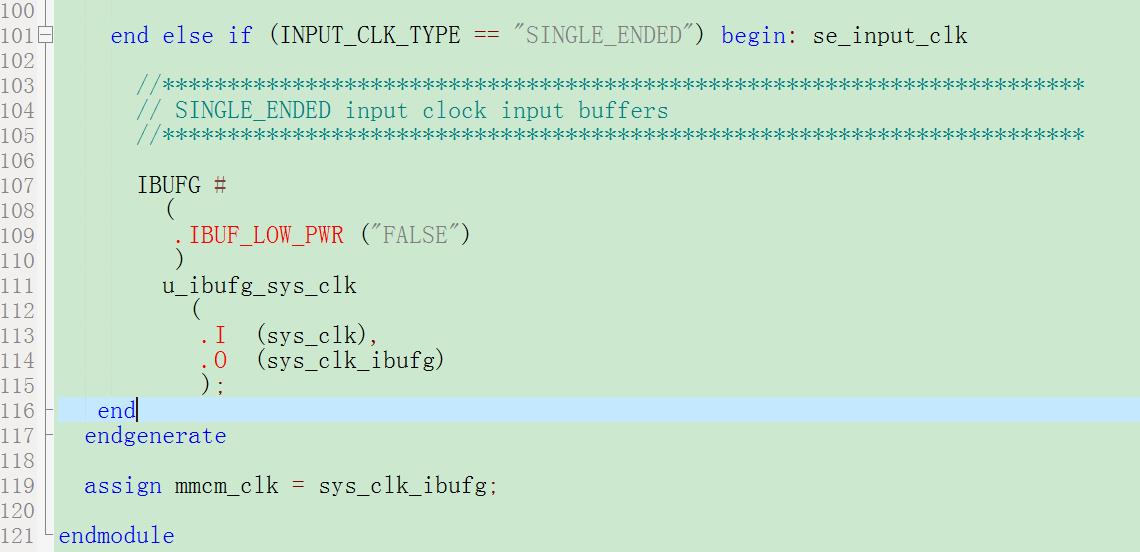

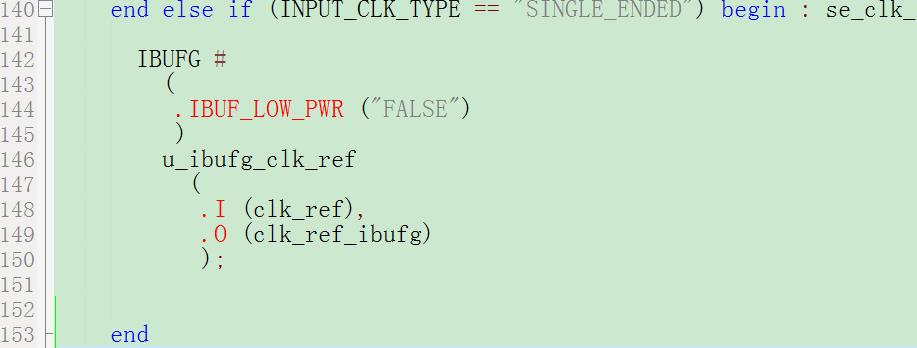

Sys_clk經過clk_ibuf 模塊之后產生出mmcm_clk。Clk_ibuf中的相關程序代碼如下:

發現sys_clk時鐘信號經過IBUFG,因此在top文件中作如下修改:

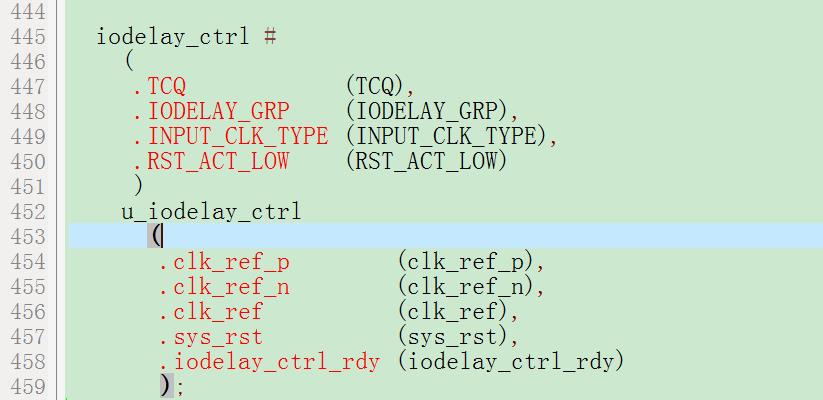

接下來查找clk_ref的問題,在top文件中與clk_ref相關的模塊如下:

Clk_ref進入了iodelay_ctrl模塊。Iodelay_ctrl模塊中的相關內容如下:

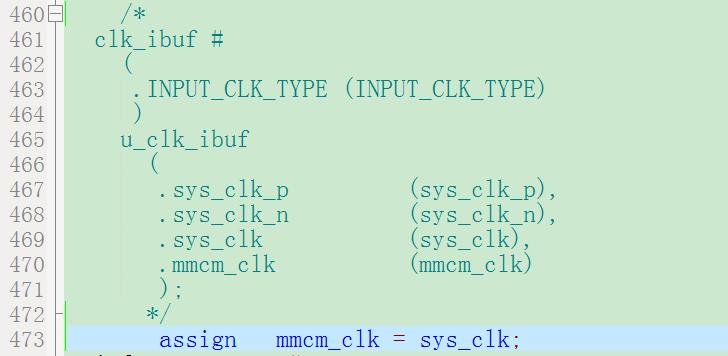

Clk_ref時鐘信號也經過了一個IBUFG,因此做如下修改:

另外,由clk_125M_p產生sys_clk和clk_ref的程序如下:

修改后編譯順利通過。

若您有高速數據采集板卡定制需求,請聯系我們:400-000-4026

關于坤馳科技:

坤馳科技是專注于高速數據采集與信號處理、高速數據存儲與記錄的高科技公司。坤馳科技為用戶提供成熟的標準高速數據采集產品與技術,也可為用戶提供定制化的高速信號采集解決方案。目前坤馳科技服務過的研究所、科研單位已達近百家。高速數據采集產品線涵蓋PCIExpress、cPCI、PXIe、VPX、USB等總線,包含高速AD、DA平臺、FPGA、DSP處理平臺,SATA/SSD、Flash存儲平臺等。

全國咨詢電話:400-000-4026