各種

高速AD采集卡大體硬件功能相同時,使用不同的FPGA時,如V5和V6系列,單就高速AD采集卡的邏輯和性能來說,帶來一些差異。通過簡單對比北京坤馳科技有限公司的使用了交織采樣技術的高性能同系列高速AD采集卡,就會很清晰的得出相關差異分析結果。

1,例如其ADQ系列高速AD采集卡的板上FPGA分為V5和V6兩個系列,在觸發功能上大部分原理是相同的,但FPGA不同的物理結構也導致了一些差異,那么差異在哪呢?

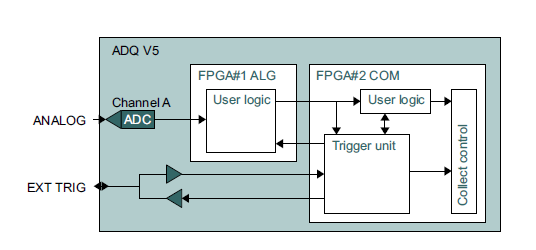

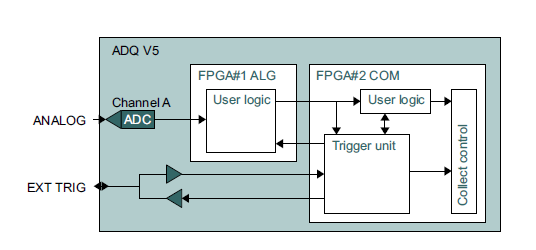

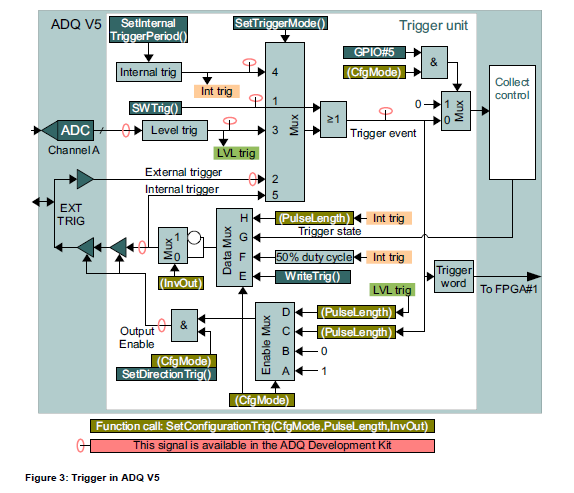

首先,V5有兩個FPGA模塊,觸發模塊在FPGA #2上, 實現觸發輸出及其他與數據采集觸發相關的功能,例如在波形平均功能使用時,也需要FPGA #2上的觸發模塊將產生的觸發信息傳到FPGA#1,2塊FPGA的物理結構給觸發帶來了傳輸、處理上的相對限制。還有,V5上觸發輸入和輸出共用相同的物理連接器。

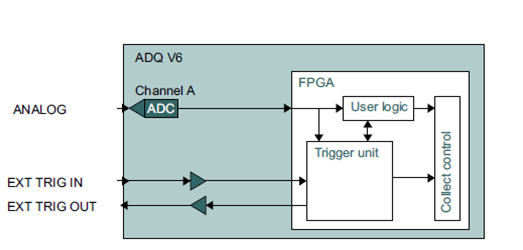

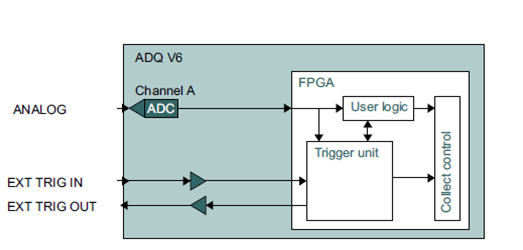

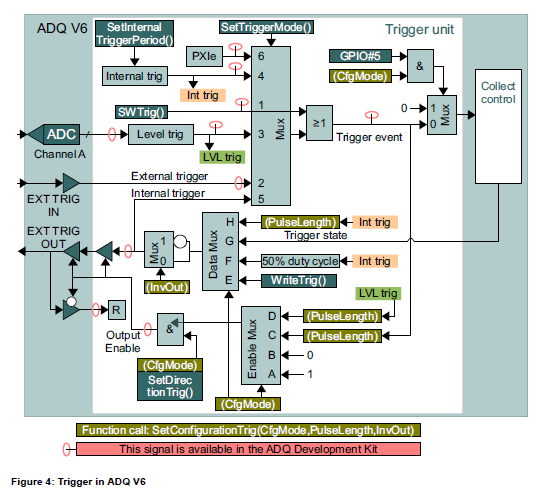

對比之下,V6,只有一塊更為強大的FPGA,各功能模塊之間的通信比V5更為直接高效,觸發輸入和觸發輸出使用不同的連接器,大大增加了靈活性。

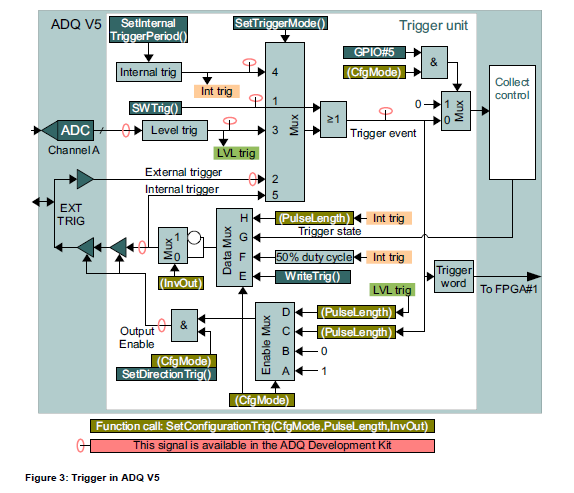

兩者觸發邏輯對比如下兩圖:

A,V5系列

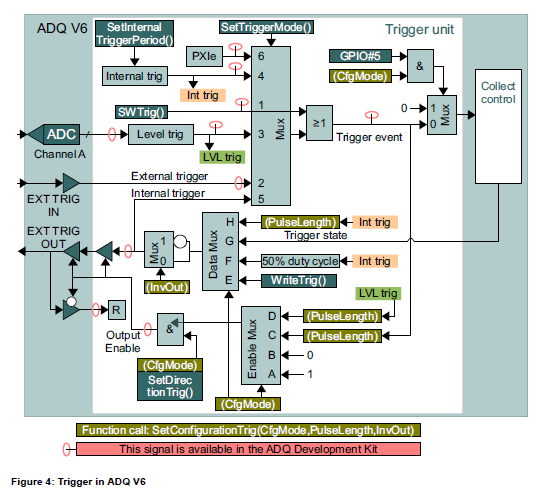

B,V6系列

2,觸發模式:

觸發器可以選擇兩種主要的觸發模式:

1, 觸發的數據流模式(triggered streaming)-適合大化的利用數據傳輸到主機的速度

2, 多段記錄模式(multi record mode)-適合大量數據的實時采集

3,觸發框圖

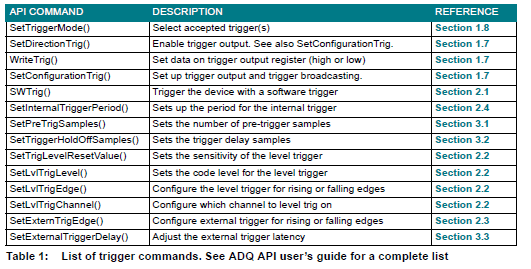

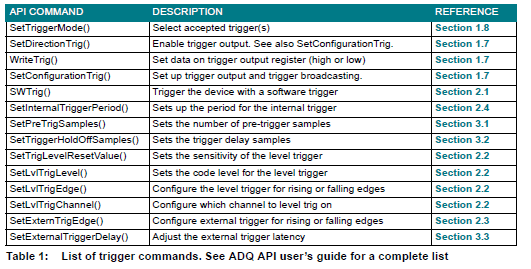

4,觸發相關的API指令

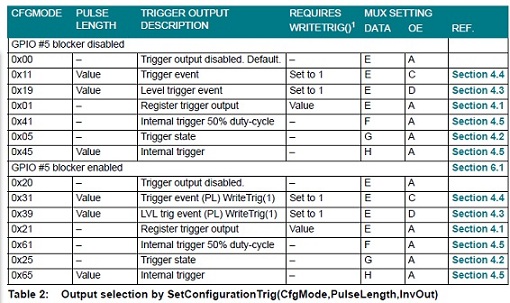

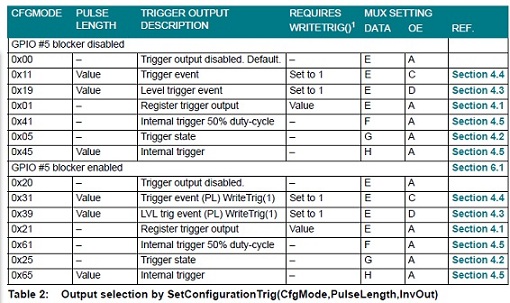

5,觸發輸出設置參考表格:

Table 2列出了觸發的相關設置,CfgMode參數控制了觸發輸出設置和GPIO#5的輸入觸發模塊功能的設置。PulseLength參數為脈沖長度設置。

Figure 4中的InvOut是反向觸發輸出參數。

使用SetConfigurationTrig()時,不需使用SetDirectionTrig()指令;WriteTrig()為寄存器觸發設置硬件寄存器的位數。

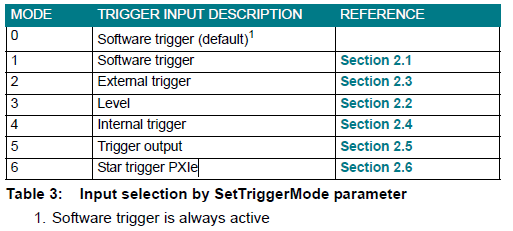

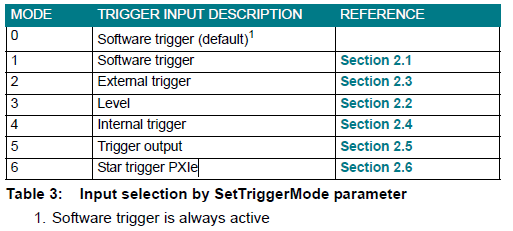

觸發輸入控制參考表格

6,采集控制設置

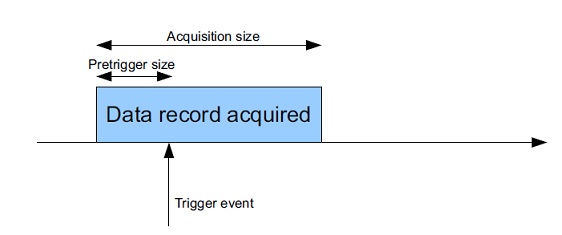

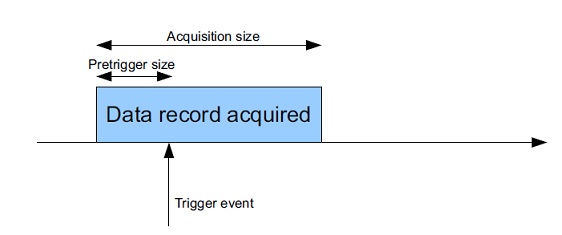

6.1 Pre-trigger

注,數據流模式(streaming mode)下,預觸發的長度是有限的,對比之下,多段記錄模式下(multi-record)高可達234個采樣點。

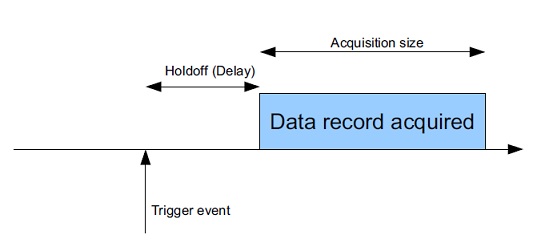

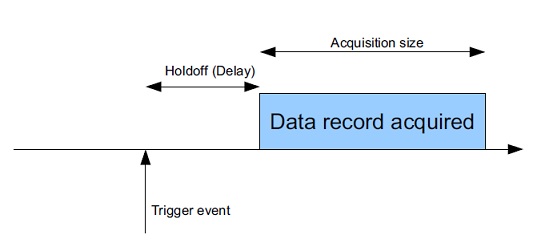

6.2 Hold-off (Delay)

延遲長度高可達234個采樣點(取決于板卡模式)

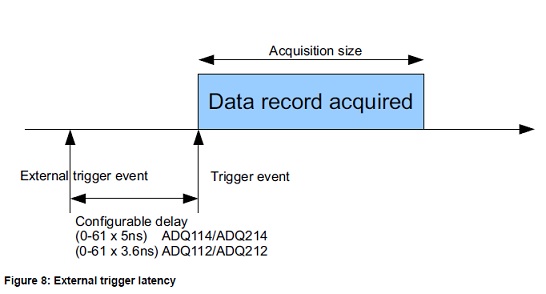

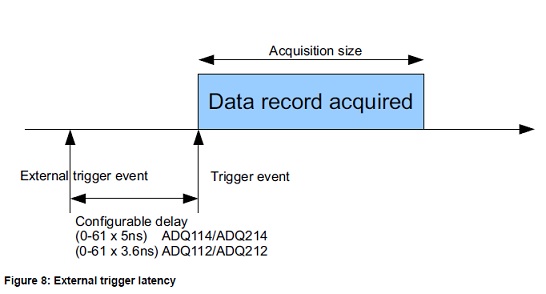

6.3 可調節外部觸發延遲(ADQ V5)

當數據從ADC經由電路傳到用戶邏輯模塊進行處理時,延遲長度可能因電路原因發生變化。為了補償這個變化,外部觸發器可相對延時基線延時一定的采樣點數。如下圖,這種效果與觸發

hold-off模式較為相似。是hold-off模式與用戶邏輯之間中間處理操作。